# EFR32xG21 Wireless Gecko Reference Manual

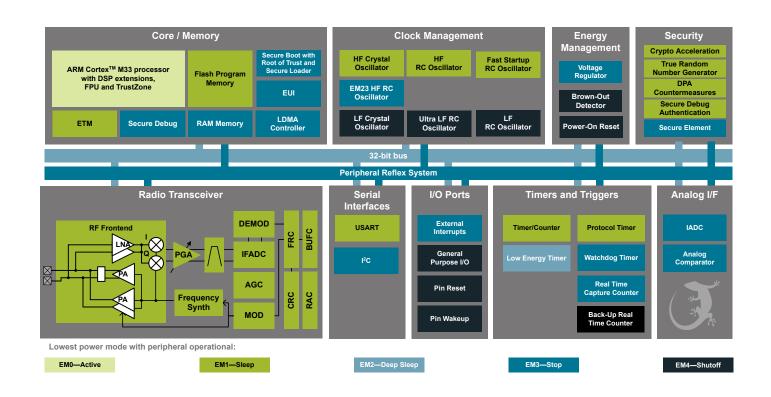

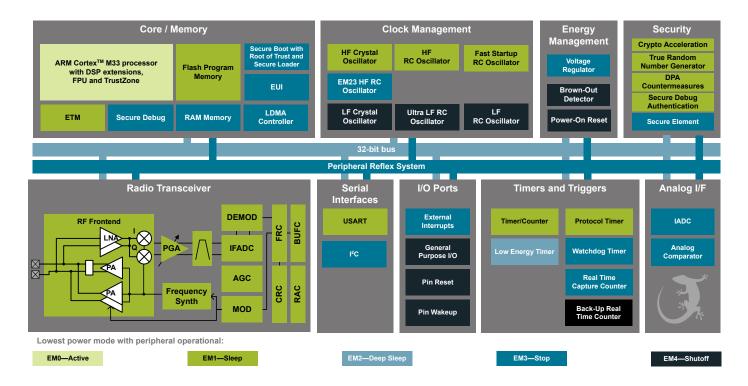

The EFR32xG21 Wireless Gecko SoC is the first device in the Series 2 Wireless Gecko Portfolio, and includes the EFR32MG21 Mighty Gecko and EFR32BG21 Blue Gecko. The EFR32xG21 improves processing capability with a Cortex M33 core and has best in class link budget while providing for lower active current for both the MCU and radio. The dedicated security core (Secure Element) provides improved cryptography and hardware security that is isolated from the main application CPU. This high performance and secure multi-protocol device supports Zigbee, Thread, and Bluetooth 5.0.

The single-die solution provides industry-leading energy efficiency, processing capability, and RF performance in a small form factor for IoT connected applications.

#### **KEY FEATURES**

- 32-bit ARM® Cortex M33 core with 80 MHz maximum operating frequency

- Scalable Memory and Radio configuration options available in QFN packaging

- Peripheral Reflex System enabling autonomous interaction of MCU peripherals

- Autonomous Hardware Crypto Accelerator and True Random Number Generator

- Multiple Integrated 2.4 GHz PAs with up to 20 dBm transmit power

# **Table of Contents**

| 1. | About This Document                                           | . 23 |

|----|---------------------------------------------------------------|------|

|    | 1.1 Introduction                                              | .23  |

|    | 1.2 Conventions                                               | .24  |

|    | 1.3 Related Documentation                                     | .25  |

| 2. | System Overview                                               | . 26 |

|    | 2.1 Introduction                                              | .27  |

|    | 2.2 Block Diagrams                                            | .28  |

|    | 2.3 MCU Features overview                                     | .29  |

|    | 2.4 Security Features                                         |      |

|    | 2.4.1 Secure Boot with Root of Trust and Secure Loader (RTSL) |      |

|    | 2.4.2 Cryptographic Accelerator                               |      |

|    | 2.4.4 Secure Debug with Lock/Unlock.                          |      |

|    | 2.4.5 DPA Countermeasures                                     | .31  |

|    | 2.4.6 Secure Key Management with PUF                          |      |

|    | 2.4.7 Anti-Tamper                                             |      |

|    | 2.5 Oscillators and Clocks                                    |      |

|    | 2.6 RF Frequency Synthesizer                                  |      |

|    | 2.7 Modulation Modes                                          |      |

|    | 2.8 Transmit Mode                                             |      |

|    | 2.9 Receive Mode                                              |      |

|    | 2.10 Data Buffering                                           |      |

|    | 2.11 Unbuffered Data Transfer                                 |      |

|    | 2.12 Frame Format Support                                     |      |

|    | 2.13 Hardware CRC Support                                     | .35  |

|    | 2.14 Convolutional Encoding / Decoding                        | .35  |

|    | 2.15 Binary Block Encoding / Decoding                         | .35  |

|    | 2.16 Timers                                                   | .36  |

|    | 2.17 RF Test Modes                                            | .36  |

| 3. | System Processor                                              | . 37 |

|    | 3.1 Introduction                                              | .37  |

|    | 3.2 Features                                                  | .38  |

|    | 3.3 Functional Description                                    | .38  |

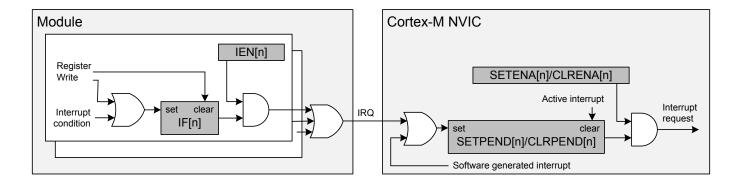

|    | 3.3.1 Interrupt Operation                                     |      |

|    | 3.3.2 TrustZone                                               |      |

|    | 3.3.3 Interrupt Request lines (IRQ)                           |      |

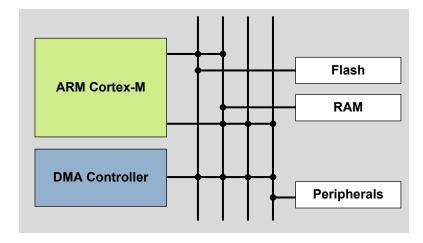

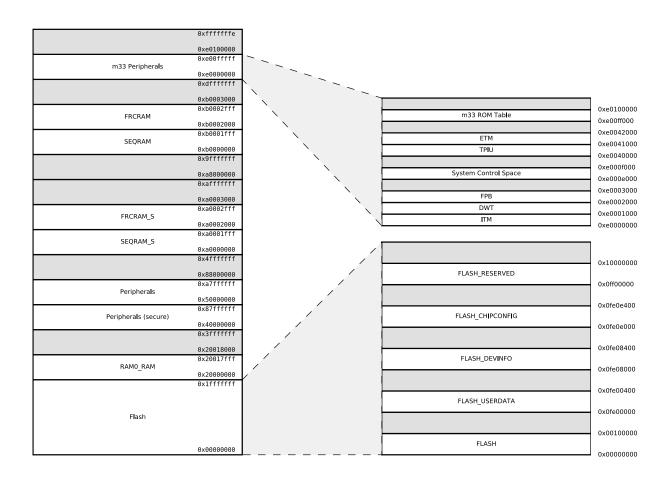

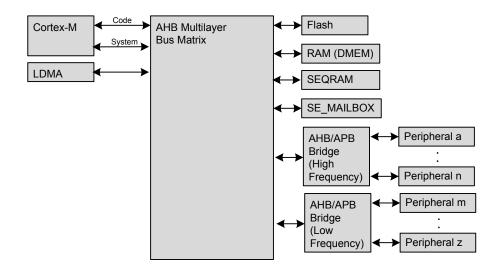

| 4  | Memory and Bus System                                         | 42   |

|    | 4.1 Introduction                       |  |      |      |      |      |   |  |   |      |  |   | .42   |

|----|----------------------------------------|--|------|------|------|------|---|--|---|------|--|---|-------|

|    | 4.2 Functional Description             |  |      |      |      |      |   |  |   |      |  |   | .43   |

|    | 4.2.1 Bus Matrix                       |  |      |      |      |      |   |  |   |      |  |   | .44   |

|    | 4.2.2 Flash                            |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 4.2.3 SRAM                             |  |      |      |      |      |   |  |   |      |  |   | .45   |

|    | 4.2.4 Peripherals                      |  |      |      |      |      |   |  |   |      |  |   | .45   |

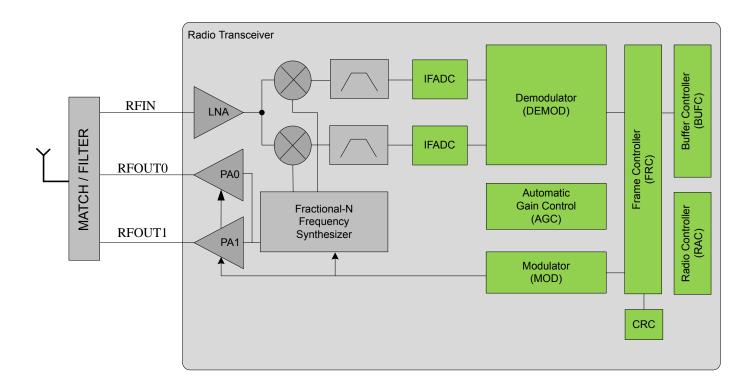

| 5. | Radio Transceiver                      |  |      |      |      |      |   |  |   |      |  |   | . 51  |

|    | 5.1 Introduction                       |  |      |      |      |      |   |  |   |      |  |   |       |

|    |                                        |  |      |      |      |      |   |  |   |      |  |   |       |

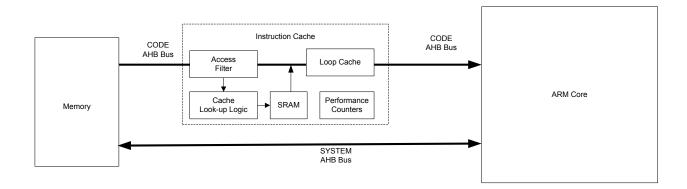

| 6. | MSC - Memory System Controller         |  |      |      |      |      |   |  | • |      |  |   | . 53  |

|    | 6.1 Introduction                       |  |      |      |      |      |   |  |   |      |  |   | .53   |

|    | 6.2 Features                           |  |      |      |      |      |   |  |   |      |  |   | .54   |

|    | 6.3 Functional Description             |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.1 Ram Configuration                |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.2 Instruction Cache                |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.3 Device Information (DI) Page .   |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.4 User Data (UD) Page Description  |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.5 Bootloader                       |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.6 Post-reset Behavior              |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.7 Flash Startup                    |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.8 Wait-states                      |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.9 Cortex-M33 If-Then Block Folding |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.3.10 Line Buffering (Prefetch)       |  |      |      |      |      |   |  |   |      |  |   | .56   |

|    | 6.3.11 Erase and Write Operations      |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.4 DEVINFO - Device Info Page         |  |      |      |      |      |   |  |   |      |  |   | .58   |

|    | 6.4.1 Register Map                     |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.4.2 Register Description             |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.5 ICACHE - Instruction Cache         |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.5.1 Cache Operation                  |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.5.2 Performance Measurement          |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.5.3 Register Map                     |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.5.4 Register Description             |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6 SYSCFG - System Configuration      |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.1 Ram Retention                    |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.2 ECC                              |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.3 RAM Wait-states                  |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.4 RAM Prefetch                     |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.5 RAM Cache                        |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.6 Software Interrupts              |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.7 Bus faults                       |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.8 Register Map                     |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.6.9 Register Description             |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.7 Register Map                       |  |      |      |      |      |   |  |   |      |  |   |       |

|    | •                                      |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.8 Register Description               |  |      |      |      |      |   |  |   |      |  |   |       |

|    | 6.8.1 MSC IPVERSION - IP version ID    |  | <br> | <br> | <br> | <br> | _ |  |   | <br> |  | _ | . 115 |

|    | 6.8.2 MSC_READCTRL - Read Control Register               | . 116              |

|----|----------------------------------------------------------|--------------------|

|    | 6.8.3 MSC_WRITECTRL - Write Control Register             | . 117              |

|    | 6.8.4 MSC_WRITECMD - Write Command Register              | . 118              |

|    | 6.8.5 MSC_ADDRB - Page Erase/Write Address Buffer        |                    |

|    | 6.8.6 MSC_WDATA - Write Data Register                    |                    |

|    | 6.8.7 MSC_STATUS - Status Register                       |                    |

|    | 6.8.8 MSC_IF - Interrupt Flag Register                   |                    |

|    | 6.8.9 MSC_IEN - Interrupt Enable Register                |                    |

|    | 6.8.10 MSC_USERDATASIZE - user data regsion size         |                    |

|    | 6.8.11 MSC_CMD - Command Register                        |                    |

|    | 6.8.12 MSC_LOCK - Configuration Lock Register            |                    |

|    | 6.8.13 MSC_MISCLOCKWORD - Mass erase lock word           |                    |

|    | 6.8.15 MSC PAGELOCK1 - Main space page 0-31 lock word    |                    |

|    | 6.8.16 MSC_PAGELOCK2 - Main space page 64-95 lock word   |                    |

|    | 6.8.17 MSC_PAGELOCK3 - Main space page 96-127 lock word. |                    |

|    | 6.8.18 MSC_TESTCTRL - Flash test control register.       |                    |

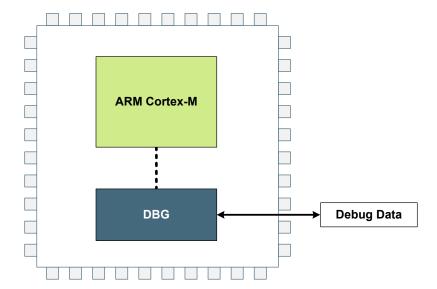

| 7  | DBG - Debug Interface                                    |                    |

| ١. | -                                                        |                    |

|    | 7.1 Introduction                                         |                    |

|    | 7.2 Features                                             |                    |

|    | 7.3 Functional Description                               |                    |

|    | 7.3.1 Debug Pins                                         |                    |

|    | 7.3.2 Embedded Trace Macrocell V3.5 (ETM)                |                    |

|    | 7.3.3 Debug and EM2/EM3                                  |                    |

|    | 7.4 DBG Register Map                                     | . 129              |

|    | 7.5 DBG Register Description                             |                    |

|    | 7.5.1 DBG_DCIWDATA - Write Data                          |                    |

|    | 7.5.2 DBG_DCIRDATA - Read Data                           |                    |

|    | 7.5.3 DBG_DCISTATUS - Status                             |                    |

|    | 7.5.4 DBG_DCIID - Identification                         |                    |

|    | 7.5.5 DBG_SYSCOM0 - Communication Status                 |                    |

|    | 7.5.7 DBG SYSPWR0 - Power Status                         |                    |

|    | 7.5.8 DBG_SYSCLK0 - Clocking Status                      |                    |

|    | 7.5.9 DBG SYSID - Identification                         |                    |

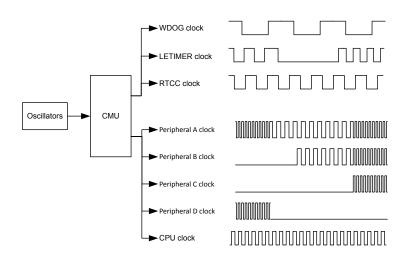

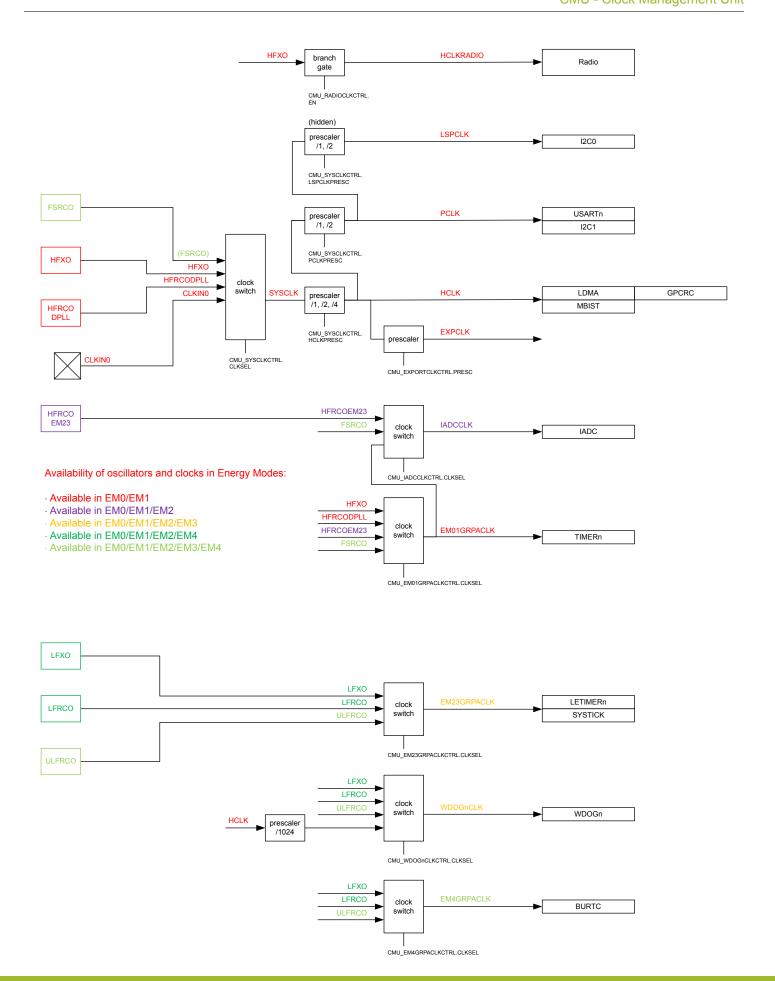

| 0  | CMU - Clock Management Unit                              |                    |

| ο. |                                                          |                    |

|    | 8.1 Introduction                                         |                    |

|    | 8.2 Features                                             |                    |

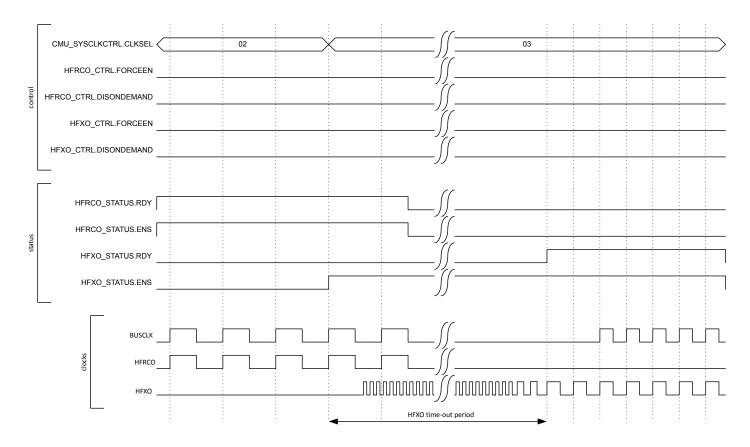

|    | 8.3 Functional Description                               |                    |

|    | 8.3.1 System Clocks                                      |                    |

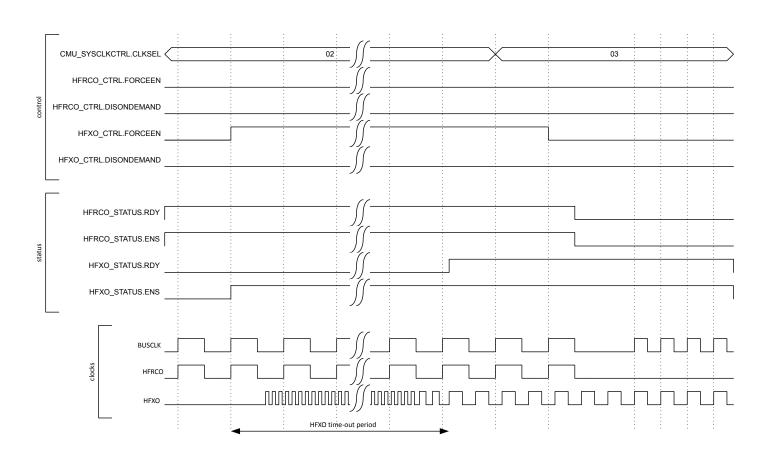

|    | 8.3.2 Switching Clock Source                             |                    |

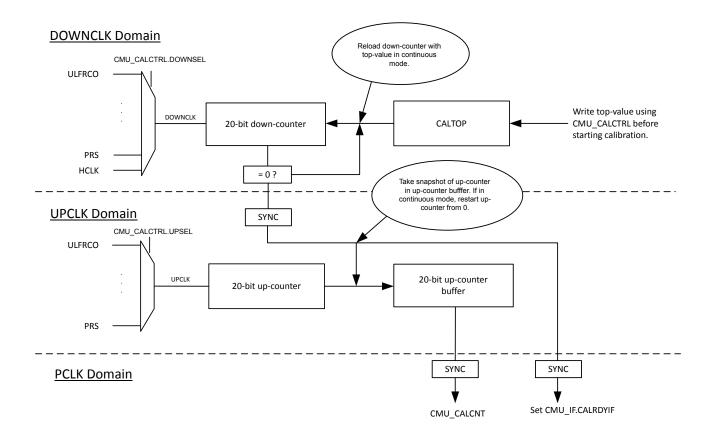

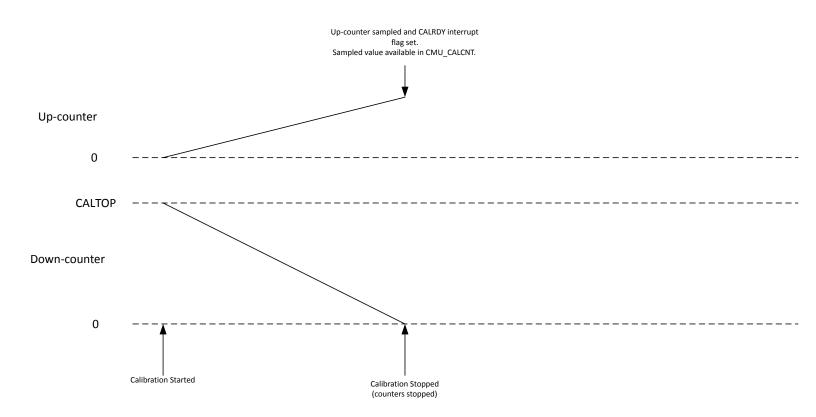

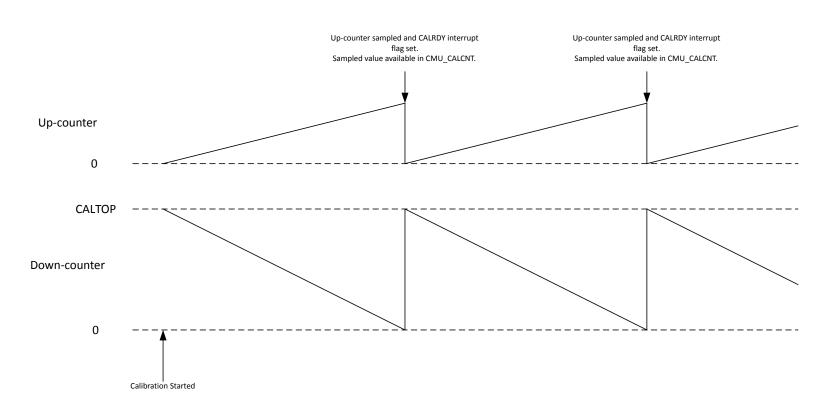

|    | 8.3.3 RC Oscillator Calibration                          |                    |

|    | 8.3.4 Energy Modes                                       |                    |

|    | 8.3.5 Clock Output on a Pin                              |                    |

|    | U.J.U CIUCK INDUL II UIII A FIII                         | . 1 <del>4</del> 9 |

|    | 8.3.7 Clock Output on PRS                                          |       |

|----|--------------------------------------------------------------------|-------|

|    | 8.3.8 Interrupts                                                   | .149  |

|    | 8.3.9 Protection                                                   | .149  |

|    | 8.4 Register Map                                                   | 150   |

|    |                                                                    |       |

|    | 8.5 Register Description                                           |       |

|    | 8.5.1 CMU_IPVERSION - IP version ID                                |       |

|    | 8.5.2 CMU_STATUS - Status Register                                 |       |

|    | 8.5.3 CMU_LOCK - Configuration Lock Register                       |       |

|    | 8.5.4 CMU_WDOGLOCK - WDOG Configuration Lock Register              | . 154 |

|    | 8.5.5 CMU_IF - Interrupt Flag Register                             | .155  |

|    | 8.5.6 CMU_IEN - Interrupt Enable Register                          | . 155 |

|    | 8.5.7 CMU_CALCMD - Calibration Command Register                    | . 156 |

|    | 8.5.8 CMU_CALCTRL - Calibration Control Register                   | . 157 |

|    | 8.5.9 CMU_CALCNT - Calibration Result Counter Register             | 158   |

|    | 8.5.10 CMU_SYSCLKCTRL - System Clock Control                       | . 159 |

|    | 8.5.11 CMU_TRACECLKCTRL - Debug Trace Clock Control                |       |

|    | 8.5.12 CMU_EXPORTCLKCTRL - Export Clock Control                    |       |

|    | 8.5.13 CMU_DPLLREFCLKCTRL - Digital PLL Reference Clock Control    |       |

|    | 8.5.14 CMU_EM01GRPACLKCTRL - EM01 Peripheral Group A Clock Control |       |

|    | 8.5.15 CMU_EM23GRPACLKCTRL - EM23 Peripheral Group A Clock Control |       |

|    | 8.5.16 CMU_EM4GRPACLKCTRL - EM4 Peripheral Group A Clock Control   |       |

|    | 8.5.17 CMU_IADCCLKCTRL - IADC Clock Control                        |       |

|    | 8.5.18 CMU_WDOG0CLKCTRL - Watchdog0 Clock Control                  |       |

|    | 8.5.19 CMU_WDOG1CLKCTRL - Watchdog1 Clock Control                  |       |

|    | 8.5.20 CMU RTCCCLKCTRL - RTCC Clock Control                        |       |

|    | 8.5.21 CMU_RADIOCLKCTRL - Radio Clock Control                      |       |

|    |                                                                    |       |

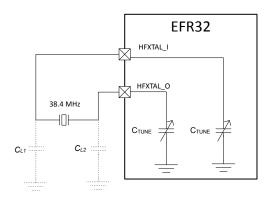

| 9. | Oscillators                                                        | .169  |

|    | 9.1 Introduction                                                   | . 169 |

|    | 9.2 HFXO - High Frequency Crystal Oscillator                       |       |

|    |                                                                    |       |

|    | 9.2.1 Introduction                                                 |       |

|    | 9.2.2 Features                                                     |       |

|    | 9.2.3 Functional Description                                       |       |

|    | 9.2.4 Register Map                                                 |       |

|    | 9.2.5 Register Description                                         | . 1/4 |

|    | 9.3 HFRCO - High-Frequency RC Oscillator                           | .184  |

|    | 9.3.1 Introduction                                                 | .184  |

|    | 9.3.2 Features                                                     | . 184 |

|    | 9.3.3 Functional Description                                       | . 184 |

|    | 9.3.4 Register Map                                                 | . 187 |

|    | 9.3.5 Register Description                                         | . 188 |

|    | 9.4 DPLL - Digital Phased Locked Loop                              | 192   |

|    | 9.4.1 Introduction                                                 |       |

|    | 9.4.2 Features                                                     |       |

|    | 9.4.3 Functional Description                                       |       |

|    | 9.4.4 Register Map                                                 |       |

|    | 9.4.5 Register Description                                         |       |

|    | 3.4.J NEGISIEI DESCHUIUH                                           | . 190 |

| 9.5 LFXO - Low-Frequency Crystal Oscillator    | 200               |

|------------------------------------------------|-------------------|

| 9.5.1 Introduction                             | 200               |

| 9.5.2 Features                                 | 200               |

| 9.5.3 Functional Description                   | 200               |

| 9.5.4 Register Map                             |                   |

| 9.5.5 Register Description                     |                   |

| 9.6 LFRCO - Low-Frequency RC Oscillator        |                   |

| 9.6.1 Introduction                             |                   |

| 9.6.2 Features                                 |                   |

| 9.6.3 Functional Description                   |                   |

| 9.6.4 Register Map                             |                   |

| 9.6.5 Register Description                     |                   |

|                                                |                   |

| 9.7 FSRCO - Fast Start RCO                     |                   |

| 9.7.1 Introduction                             |                   |

| 9.7.2 Features                                 |                   |

| 9.7.3 Functional Description                   |                   |

| 9.7.4 Register Map                             |                   |

| 9.7.5 Register Description                     |                   |

| 9.8 ULFRCO - Ultra Low Frequency RC Oscillator | .217              |

| 9.8.1 Introduction                             | 217               |

| 9.8.2 Features                                 | 217               |

| 9.8.3 Functional Description                   | 217               |

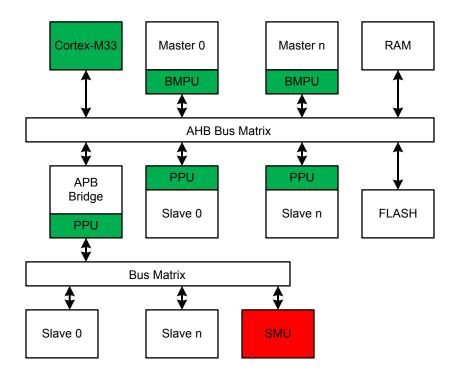

| 0. SMU - Security Management Unit              | 218               |

| 10.1 Introduction                              |                   |

|                                                |                   |

| 10.2 Features                                  |                   |

| 10.3 Functional Description                    |                   |

| 10.3.1 Bus Level Security                      |                   |

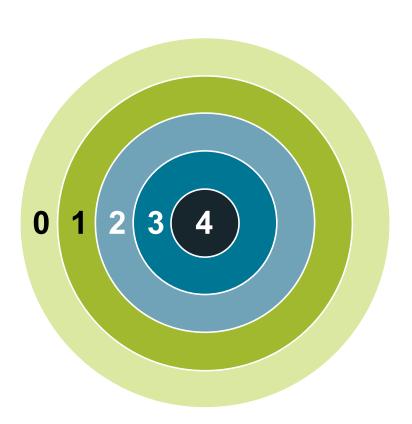

| 10.3.2 Privileged Access Control               |                   |

| 10.3.3 Secure Access Control                   |                   |

| 10.3.4 ARM TrustZone                           |                   |

| 10.3.5 Configuring Masters                     |                   |

| 10.3.6 Configuring Peripherals                 |                   |

| 10.3.7 Configuring Memory                      | .222              |

| 10.3.8 Cortex-M33 Integration                  | .222              |

| 10.3.9 Exception Handling                      |                   |

| 10.3.10 SMU Lock                               | .223              |

| 10.4 Register Map                              | . 224             |

| 10.5 Register Description                      | 226               |

| 10.5.1 SMU IPVERSION - IP Version              |                   |

| 10.5.2 SMU_STATUS - Status Register            |                   |

|                                                | 227               |

| <del>-</del>                                   |                   |

| 10.5.3 SMU_LOCK - Lock Register                | 227               |

| 10.5.3 SMU_LOCK - Lock Register                | 227<br>228        |

| 10.5.3 SMU_LOCK - Lock Register                | 227<br>228<br>229 |

| 10.5.8 SMU_PPUPATD1 - Privileged Access                        | .233  |

|----------------------------------------------------------------|-------|

| 10.5.9 SMU_PPUSATD0 - Secure Access                            | . 235 |

| 10.5.10 SMU_PPUSATD1 - Secure Access                           | 237   |

| 10.5.11 SMU_PPUFS - Fault Status                               | .238  |

| 10.5.12 SMU_BMPUPATD0 - Privileged Attribute                   | 239   |

| 10.5.13 SMU_BMPUSATD0 - Secure Attribute                       | 240   |

| 10.5.14 SMU_BMPUFS - Fault Status                              | 241   |

| 10.5.15 SMU_BMPUFSADDR - Fault Status Address                  | 241   |

| 10.5.16 SMU_ESAURTYPES0 - Region Types 0                       | 242   |

| 10.5.17 SMU_ESAURTYPES1 - Region Types 1                       | 242   |

| 10.5.18 SMU_ESAUMRB01 - Movable Region Boundary                | . 243 |

| 10.5.19 SMU_ESAUMRB12 - Movable Region Boundary                | . 243 |

| 10.5.20 SMU_ESAUMRB45 - Movable Region Boundary                | . 244 |

| 10.5.21 SMU_ESAUMRB56 - Movable Region Boundary                | . 244 |

| 11. SE - Secure Element Subsystem                              | 245   |

| 11.1 Introduction                                              | 245   |

| 11.2 Security Features                                         | 245   |

| 11.2.1 Security Features Overview                              |       |

| 11.2.2 Secure Boot with Root of Trust and Secure Loader (RTSL) |       |

| 11.2.3 Secure Debug                                            |       |

| 11.2.4 Cryptographic Accelerator                               |       |

| 11.2.5 True Random Number Generation                           |       |

| 11.2.6 Secure Key Management with PUF                          |       |

| 11.2.7 Anti-Tamper                                             | 248   |

| 11.2.8 Secure Attestation                                      | 248   |

| 11.3 SE Mailbox                                                | 248   |

| 11.3.1 Sending Commands                                        |       |

| 11.3.2 Receiving Responses                                     |       |

| 11.3.3 Register Map                                            |       |

| 11.3.4 Register Description                                    |       |

| 12. EMU - Energy Management Unit                               |       |

|                                                                |       |

| 12.1 Introduction                                              |       |

| 12.2 Features                                                  |       |

| 12.3 Functional Description                                    |       |

| 12.3.1 Energy Modes                                            |       |

| 12.3.2 Entering Low Energy Modes                               |       |

| 12.3.3 Exiting a Low Energy Mode                               |       |

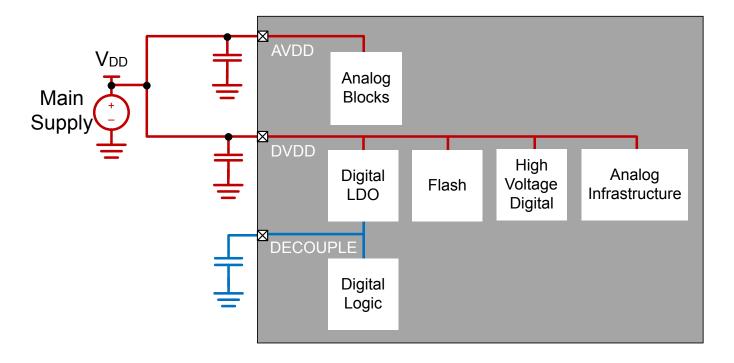

| 12.3.4 Power Domains                                           |       |

| 12.3.5 Brown Out Detector (BOD)                                |       |

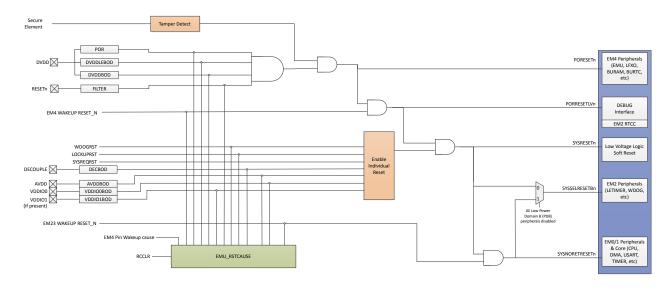

| 12.3.6 Reset Management Unit                                   |       |

| 12.3.7 Temperature Sensor                                      |       |

| 12.3.8 Register Resets                                         |       |

| 12.3.9 Register Locks                                          | . 268 |

| 12.4 Register Map                                              | 269   |

| 12.5 Register Description                                      | 271   |

| 12.5.1 EMU_DECBOD - DECOUPLE LVBOD Control register                           | 271   |

|-------------------------------------------------------------------------------|-------|

| 12.5.2 EMU_BOD3SENSE - BOD3SENSE Control register                             |       |

| 12.5.3 EMU_LOCK - EMU Configuration lock register                             | 272   |

| 12.5.4 EMU_IF - Interrupt Flags                                               | 273   |

| 12.5.5 EMU_IEN - Interrupt Enables                                            | .274  |

| 12.5.6 EMU_EM4CTRL - EM4 Control                                              |       |

| 12.5.7 EMU_CMD - EMU Command register                                         |       |

| 12.5.8 EMU_CTRL - EMU Control register                                        |       |

| 12.5.9 EMU_TEMPLIMITS - EMU Temperature thresholds                            | 278   |

| 12.5.10 EMU_STATUS - EMU Status register                                      |       |

| 12.5.11 EMU_TEMP - Temperature                                                |       |

| 12.5.12 EMU_RSTCTRL - Reset Management Control register                       |       |

| 12.5.13 EMU_RSTCAUSE - Reset cause                                            |       |

| 12.5.14 EMU_DGIF - Interrupt Flags Debug                                      | 284   |

| 12.5.15 EMU_DGIEN - Interrupt Enables Debug                                   |       |

| 12.5.16 EMU_SEIF - Interrupt Flags Secure Element                             |       |

| 12.5.17 EMU_SEIEN - Interrupt Enables Secure Elements                         |       |

|                                                                               |       |

| 13. PRS - Peripheral Reflex System ....................................       | 287   |

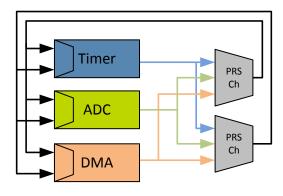

| 13.1 Introduction                                                             | 287   |

| 13.2 Features                                                                 | 287   |

| 13.3 Functional Description                                                   | . 288 |

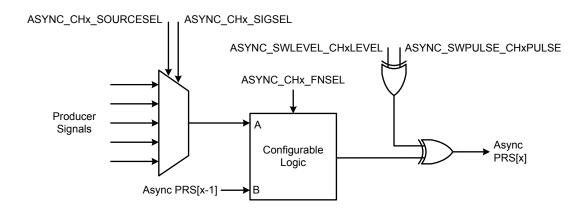

| 13.3.1 Asynchronous Channel Functions.                                        |       |

| 13.3.2 Configurable Logic                                                     |       |

| 13.3.3 Producers                                                              |       |

| 13.3.4 Consumers                                                              |       |

| 13.4 Register Map                                                             |       |

|                                                                               |       |

| 13.5 Register Description                                                     |       |

| 13.5.1 PRS_IPVERSION - IP version ID                                          |       |

| 13.5.2 PRS_ASYNC_SWPULSE - Software Pulse Register                            |       |

| 13.5.3 PRS_ASYNC_SWLEVEL - Software Level Register                            |       |

| 13.5.4 PRS_ASYNC_PEEK - Async Channel Values                                  |       |

| 13.5.5 PRS_SYNC_PEEK - Sync Channel Values                                    |       |

| 13.5.6 PRS_ASYNC_CHx_CTRL - Async Channel Control Register                    |       |

| 13.5.7 PRS_SYNC_CHx_CTRL - Sync Channel Control Register                      |       |

| 13.5.8 PRS_CONSUMER_CMU_CALDN - CMU CALDN Consumer Selection                  |       |

| 13.5.9 PRS_CONSUMER_CMU_CALUP - CMU CALUP Consumer Selection                  |       |

| 13.5.10 PRS_CONSUMER_IADC0_SCANTRIGGER - IADC0 SCANTRIGGER Consumer Selection | 317   |

| 13.5.11 PRS_CONSUMER_IADC0_SINGLETRIGGER - IADC0 SINGLETRIGGER Consumer       |       |

| Selection                                                                     |       |

| 13.5.12 PRS_CONSUMER_LDMAXBAR_DMAREQ0 - DMAREQ0 Consumer Selection            |       |

| 13.5.13 PRS_CONSUMER_LDMAXBAR_DMAREQ1 - DMAREQ1 Consumer Selection            |       |

| 13.5.14 PRS_CONSUMER_LETIMER0_CLEAR - LETIMER CLEAR Consumer Selection        | 319   |

| 13.5.15 PRS_CONSUMER_LETIMER0_START - LETIMER START Consumer Selection        |       |

| 13.5.16 PRS_CONSUMER_LETIMER0_STOP - LETIMER STOP Consumer Selection          | 320   |

| 13.5.17 PRS_CONSUMER_MODEM_DIN - MODEM DIN Consumer Selection                 |       |

| 13.5.18 PRS_CONSUMER_RAC_CLR - RAC CLR Consumer Selection                     | 321   |

| 13.5.19    | PRS_CONSUMER_RAC_FORCETX - RAC FORCETX Consumer Selection       | . 321        |

|------------|-----------------------------------------------------------------|--------------|

| 13.5.20    | PRS_CONSUMER_RAC_RXDIS - RAC RXDIS Consumer Selection           | .322         |

| 13.5.21    | PRS_CONSUMER_RAC_RXEN - RAC RXEN Consumer Selection             | . 322        |

|            | PRS_CONSUMER_RAC_SEQ - RAC SEQ Consumer Selection               |              |

|            | PRS_CONSUMER_RAC_TXEN - RAC TXEN Consumer Selection             | . 323        |

|            | PRS_CONSUMER_RTCC_CC0 - RTCC CC0 Consumer Selection             |              |

|            | PRS_CONSUMER_RTCC_CC1 - RTCC CC1 Consumer Selection             |              |

|            | PRS_CONSUMER_RTCC_CC2 - RTCC CC2 Consumer Selection             |              |

|            |                                                                 | . 325        |

|            | PRS CONSUMER SE TAMPERSRC1 - SE TAMPERSRC1 Consumer Selection   | . 326        |

|            |                                                                 | . 326        |

|            | PRS_CONSUMER_SE_TAMPERSRC3 - SE TAMPERSRC3 Consumer Selection   | . 327        |

|            |                                                                 | . 327        |

|            |                                                                 |              |

|            | PRS_CONSUMER_SE_TAMPERSRC5 - SE TAMPERSRC5 Consumer Selection . | . 328        |

|            | PRS_CONSUMER_SE_TAMPERSRC6 - SE TAMPERSRC6 Consumer Selection . | . 328        |

|            | PRS_CONSUMER_SE_TAMPERSRC7 - SE TAMPERSRC7 Consumer Selection . | . 329        |

|            |                                                                 | . 329        |

|            | <del>-</del>                                                    | . 330        |

|            | PRS_CONSUMER_CORE_CTIIN2 - CTI2 Consumer Selection              | . 330        |

|            |                                                                 | . 331        |

|            | PRS_CONSUMER_CORE_M33RXEV - M33 Consumer Selection              | . 331        |

|            | PRS_CONSUMER_TIMER0_CC0 - TIMER0 CC0 Consumer Selection         |              |

| 13.5.41    | PRS_CONSUMER_TIMER0_CC1 - TIMER0 CC1 Consumer Selection         | . 332        |

| 13.5.42    | PRS_CONSUMER_TIMER0_CC2 - TIMER0 CC2 Consumer Selection         | . 333        |

| 13.5.43    | PRS_CONSUMER_TIMER0_DTI - TIMER0 DTI Consumer Selection         | . 333        |

| 13.5.44    | PRS_CONSUMER_TIMER0_DTIFS1 - TIMER0 DTIFS1 Consumer Selection   | .334         |

| 13.5.45    | PRS_CONSUMER_TIMER0_DTIFS2 - TIMER0 DTIFS2 Consumer Selection   | .334         |

| 13.5.46    | PRS_CONSUMER_TIMER1_CC0 - TIMER1 CC0 Consumer Selection         | . 335        |

| 13.5.47    | PRS_CONSUMER_TIMER1_CC1 - TIMER1 CC1 Consumer Selection         | . 335        |

| 13.5.48    | PRS_CONSUMER_TIMER1_CC2 - TIMER1 CC2 Consumer Selection         | . 336        |

| 13.5.49    | PRS_CONSUMER_TIMER1_DTI - TIMER1 DTI Consumer Selection         | . 336        |

| 13.5.50    | PRS_CONSUMER_TIMER1_DTIFS1 - TIMER1 DTIFS1 Consumer Selection   | .337         |

| 13.5.51    | PRS_CONSUMER_TIMER1_DTIFS2 - TIMER1 DTIFS2 Consumer Selection   | .337         |

| 13.5.52    | PRS_CONSUMER_TIMER2_CC0 - TIMER2 CC0 Consumer Selection         | . 338        |

| 13.5.53    | PRS_CONSUMER_TIMER2_CC1 - TIMER2 CC1 Consumer Selection         | . 338        |

| 13.5.54    | PRS_CONSUMER_TIMER2_CC2 - TIMER2 CC2 Consumer Selection         | . 339        |

|            | PRS_CONSUMER_TIMER2_DTI - TIMER2 DTI Consumer Selection         |              |

|            | PRS CONSUMER TIMER2 DTIFS1 - TIMER2 DTIFS1 Consumer Selection   | .340         |

|            | PRS CONSUMER TIMER2 DTIFS2 - TIMER2 DTIFS2 Consumer Selection   | .340         |

|            | PRS_CONSUMER_TIMER3_CC0 - TIMER3 CC0 Consumer Selection         |              |

|            | PRS_CONSUMER_TIMER3_CC1 - TIMER3 CC1 Consumer Selection         |              |

|            | PRS CONSUMER TIMER3 CC2 - TIMER3 CC2 Consumer Selection         |              |

|            | PRS CONSUMER TIMER3 DTI - TIMER3 DTI Consumer Selection         |              |

|            | PRS CONSUMER TIMER3 DTIFS1 - TIMER3 DTIFS1 Consumer Selection   |              |

|            | PRS_CONSUMER_TIMER3_DTIFS2 - TIMER3 DTIFS2 Consumer Selection   |              |

|            | PRS CONSUMER USARTO CLK - USARTO CLK Consumer Selection         |              |

|            | PRS CONSUMER USARTO IR - USARTO IR Consumer Selection           |              |

|            | PRS_CONSUMER_USARTO_IR - USARTO IR Consumer Selection           | . 344<br>345 |

| 1.3 (3 (2) | EING GAMGUNIER UGARTU RA - UGARTU RA GUISUITEL BELECTIOU        | .04:0        |

| 13.5.67 PRS_CONSUMER_USART0_TRIGGER - USART0 TRIGGER Consumer Selection | 345 |

|-------------------------------------------------------------------------|-----|

| 13.5.68 PRS_CONSUMER_USART1_CLK - USART1 CLK Consumer Selection         | 346 |

| 13.5.69 PRS_CONSUMER_USART1_IR - USART1 IR Consumer Selection           | 346 |

| 13.5.70 PRS_CONSUMER_USART1_RX - USART1 RX Consumer Selection           | 347 |

| 13.5.71 PRS_CONSUMER_USART1_TRIGGER - USART1 TRIGGER Consumer Selection | 347 |

| 13.5.72 PRS_CONSUMER_USART2_CLK - USART2 CLK Consumer Selection         | 348 |

| 13.5.73 PRS_CONSUMER_USART2_IR - USART2 IR Consumer Selection           | 348 |

| 13.5.74 PRS_CONSUMER_USART2_RX - USART2 RX Consumer Selection           | 349 |

| 13.5.75 PRS_CONSUMER_USART2_TRIGGER - USART2 TRIGGER Consumer Selection | 349 |

| 13.5.76 PRS_CONSUMER_WDOG0_SRC0 - WDOG0 SRC0 Consumer Selection         | 350 |

|                                                                         | 350 |

|                                                                         | 351 |

| 13.5.79 PRS_CONSUMER_WDOG1_SRC1 - WDOG1 SRC1 Consumer Selection         | 351 |

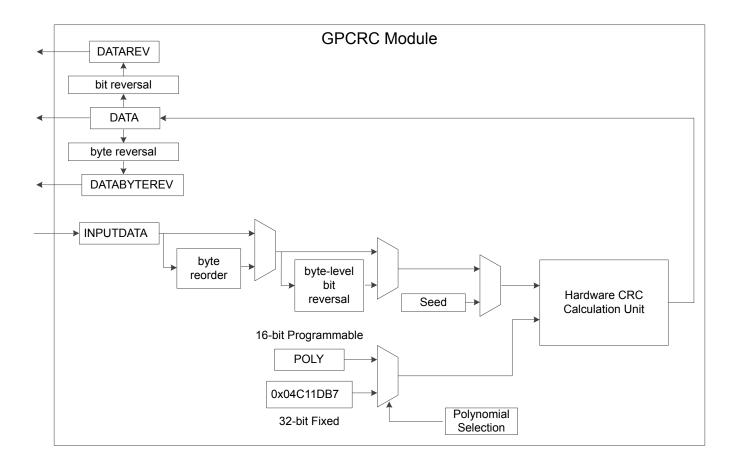

| 14. GPCRC - General Purpose Cyclic Redundancy Check                     | 352 |

| 14.1 Introduction                                                       | 352 |

| 14.2 Features                                                           | 352 |

| 14.3 Functional Description                                             | 353 |

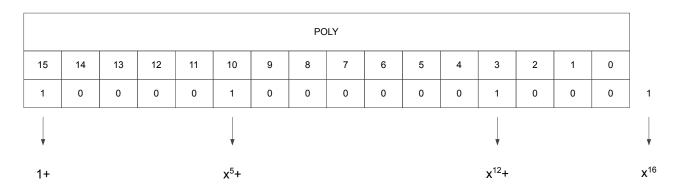

| 14.3.1 Polynomial Specification                                         | 354 |

| 14.3.2 Input and Output Specification                                   | 354 |

| 14.3.3 Initialization                                                   | 354 |

| 14.3.4 DMA Usage                                                        | 354 |

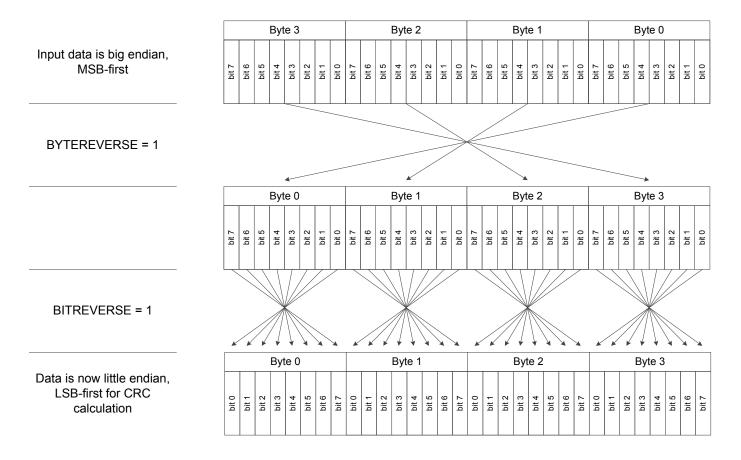

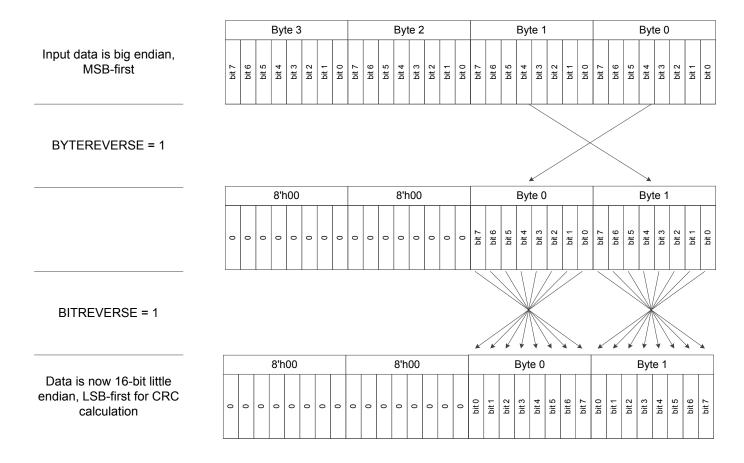

| 14.3.5 Byte-Level Bit Reversal and Byte Reordering                      | 355 |

| 14.4 Register Map                                                       | 358 |

| 14.5 Register Description                                               | 359 |

| 14.5.1 GPCRC_IPVERSION - IP Version ID                                  | 359 |

| 14.5.2 GPCRC_EN - CRC Enable                                            | 360 |

| 14.5.3 GPCRC_CTRL - Control Register                                    | 361 |

| 14.5.4 GPCRC_CMD - Command Register                                     | 362 |

| 14.5.5 GPCRC_INIT - CRC Init Value                                      | 362 |

| 14.5.6 GPCRC_POLY - CRC Polynomial Value                                | 363 |

| 14.5.7 GPCRC_INPUTDATA - Input 32-bit Data Register                     | 363 |

| 14.5.8 GPCRC_INPUTDATAHWORD - Input 16-bit Data Register                | 364 |

| 14.5.9 GPCRC_INPUTDATABYTE - Input 8-bit Data Register                  | 364 |

| 14.5.10 GPCRC_DATA - CRC Data Register                                  | 365 |

| 14.5.11 GPCRC_DATAREV - CRC Data Reverse Register                       | 365 |

| 14.5.12 GPCRC_DATABYTEREV - CRC Data Byte Reverse Register              | 366 |

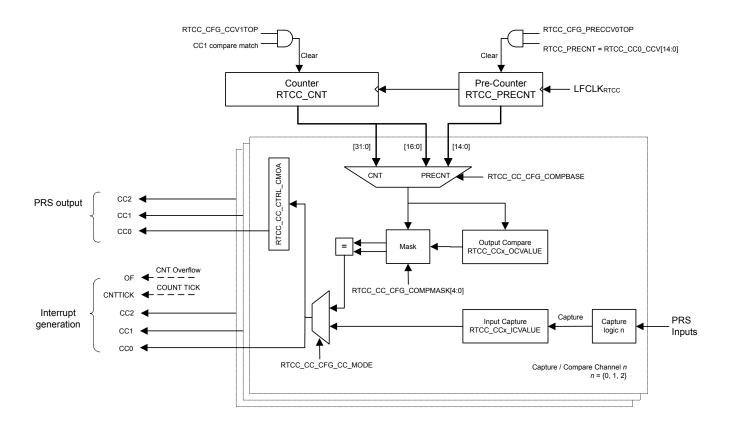

| 15. RTCC - Real Time Clock with Capture                                 | 367 |

| 15.1 Introduction                                                       | 367 |

| 15.2 Features                                                           | 367 |

| 15.3 Functional Description                                             | 368 |

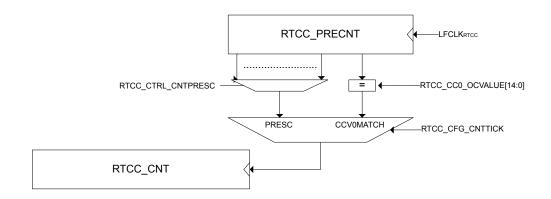

| 15.3.1 RTCC Counter                                                     | 369 |

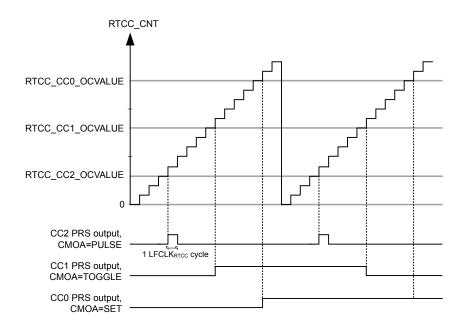

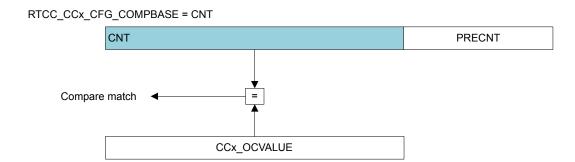

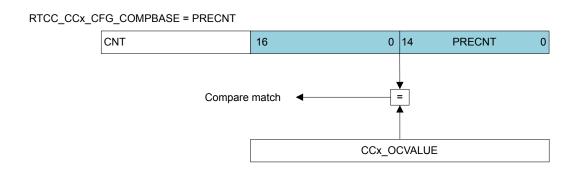

| 15.3.2 Capture/Compare Channels                                         | 371 |

| 15.3.3 Interrupts and PRS Output                                        |     |

| 15.3.4 Register Lock                                                    | 373 |

| 15.3.5 Programmer's Model                                               | 373 |

| 15.3.6 E                                                                                                                                 | Debug Features and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br>. 373                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 15.4 Regis                                                                                                                               | ister Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>. 374                                                                                       |

| 15.5.1 F<br>15.5.2 F<br>15.5.3 F<br>15.5.4 F<br>15.5.6 F<br>15.5.7 F<br>15.5.8 F<br>15.5.9 F<br>15.5.10<br>15.5.11<br>15.5.12<br>15.5.13 | Ister Description .  RTCC_IPVERSION - IP VERSION  RTCC_EN - Module Enable Register  RTCC_CFG - Configuration Register  RTCC_CMD - Command Register  RTCC_STATUS - Status register  RTCC_IF - RTCC Interrupt Flags  RTCC_IEN - Interrupt Enable Register  RTCC_PRECNT - Pre-Counter Value Register  RTCC_CNT - Counter Value Register  RTCC_COMBCNT - Combined Pre-Counter and Counter Valu  RTCC_SYNCBUSY - Synchronization Busy Register  RTCC_LOCK - Configuration Lock Register  RTCC_CCx_CTRL - CC Channel Control Register  RTCC_CCx_OCVALUE - Output Compare Value Register  RTCC_CCX_ICVALUE - Input Capture Value Register | .376<br>.377<br>.378<br>.379<br>.380<br>.381<br>.381<br>.382<br>.383<br>.383<br>.383            |

|                                                                                                                                          | - Back-Up Real Time Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                 |

|                                                                                                                                          | duction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 |

|                                                                                                                                          | ures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 |

|                                                                                                                                          | ctional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                 |

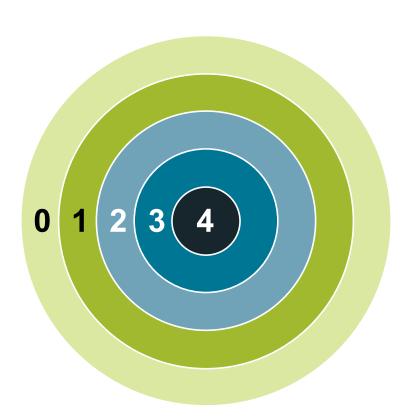

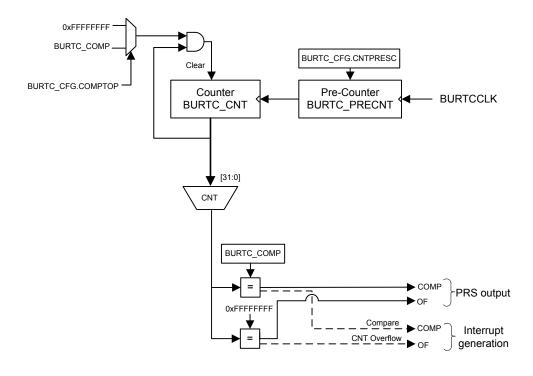

| 16.3.1 C<br>16.3.2 C<br>16.3.3 E<br>16.3.4 C<br>16.3.5 C<br>16.3.6 H                                                                     | Clock Selection Configuration Debug Features and Description Counter Compare Channel Interrupts Register Lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br><br>. 387<br>. 387<br>. 387<br>. 388<br>. 388<br>. 389                                      |

| 16.4 Regis                                                                                                                               | ister Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>. 390                                                                                       |

| 16.5.1 E<br>16.5.2 E<br>16.5.3 E<br>16.5.4 E<br>16.5.6 E<br>16.5.7 E<br>16.5.8 E<br>16.5.9 E<br>16.5.10<br>16.5.11                       | Ster Description .  BURTC_IPVERSION - IP version ID .  BURTC_EN - Module Enable Register .  BURTC_CFG - Configuration Register .  BURTC_CMD - Command Register .  BURTC_STATUS - Status Register .  BURTC_IF - Interrupt Flag Register .  BURTC_IEN - Interrupt Enable Register .  BURTC_PRECNT - Pre-Counter Value Register .  BURTC_CNT - Counter Value Register .  BURTC_CNT - Counter Value Register .  BURTC_SYNCBUSY - Synchronization Busy Register .  BURTC_LOCK - Configuration Lock Register .                                                                                                                           | . 391<br>. 392<br>. 393<br>. 394<br>. 395<br>. 395<br>. 396<br>. 397<br>. 397<br>. 398<br>. 399 |

|                                                                                                                                          | BURTC_COMP - Compare Value Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <br>. 399<br><b>400</b>                                                                         |

| T/. BUKAM                                                                                                                                | L-BACKUD KAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>400                                                                                         |

|     | 17.1 Introduction                                                  | 400        |

|-----|--------------------------------------------------------------------|------------|

|     | 17.2 Functional Description                                        | . 400      |

|     | 17.3 Register Map                                                  | . 400      |

|     | 17.4 Register Description                                          | 401        |

|     | 17.4.1 BURAM_RETx_REG - Retention Register                         | 401        |

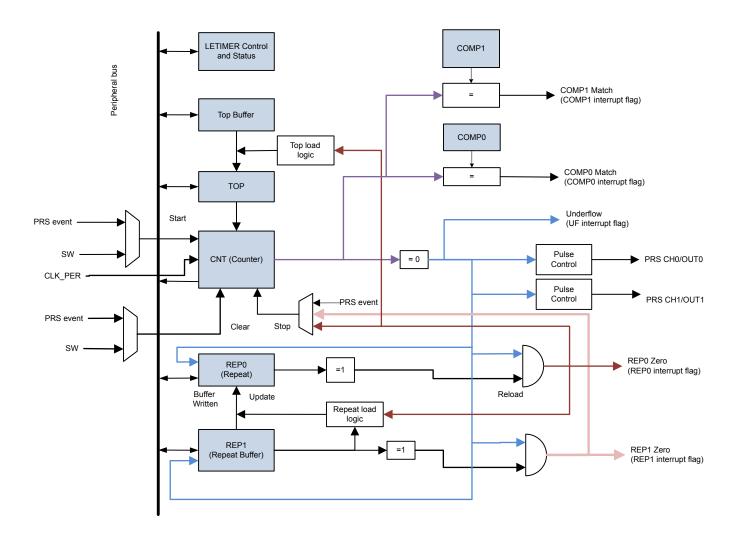

| 18. | .LETIMER - Low Energy Timer....................................    | 402        |

|     | 18.1 Introduction                                                  | 402        |

|     | 18.2 Features                                                      | 402        |

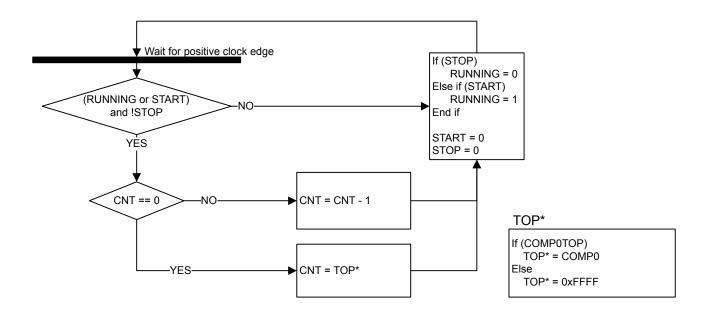

|     | 18.3 Functional Description                                        | . 403      |

|     | 18.3.1 Internal Overview                                           |            |

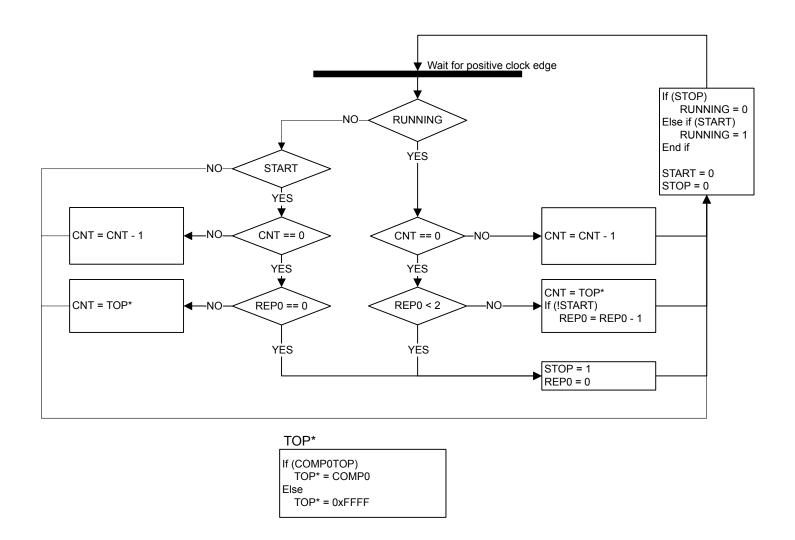

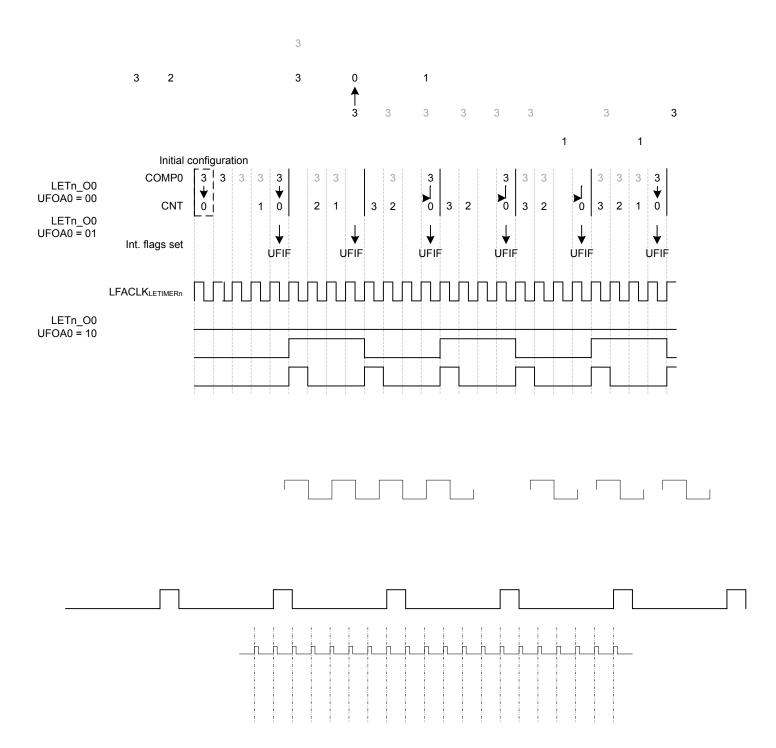

|     | 18.3.2 Free Running Mode                                           |            |

|     | 18.3.3 One-shot Mode                                               |            |

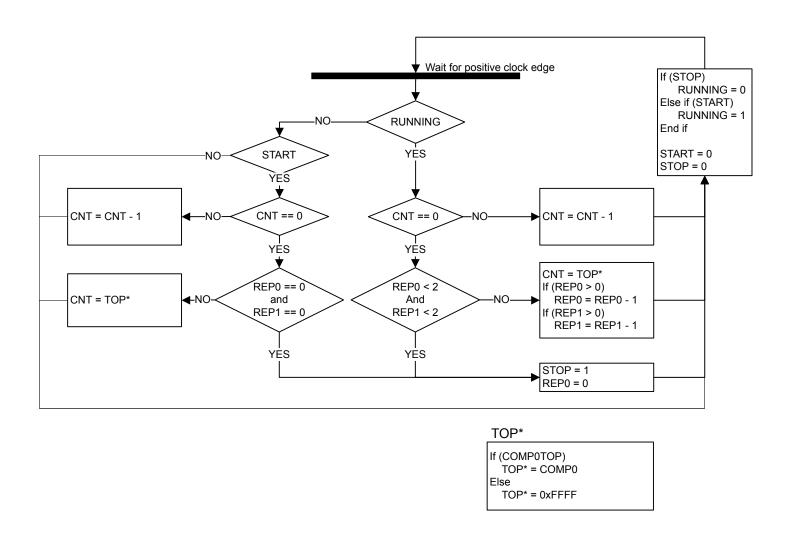

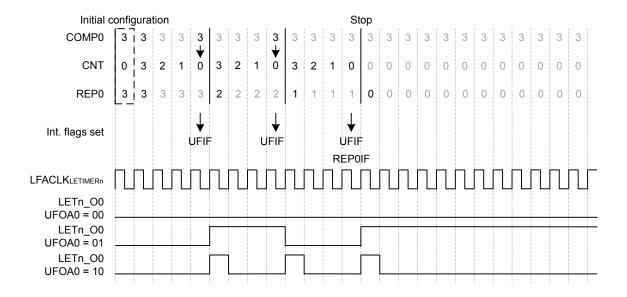

|     | 18.3.5 Double Mode                                                 |            |

|     | 18.4 Clock Frequency                                               |            |

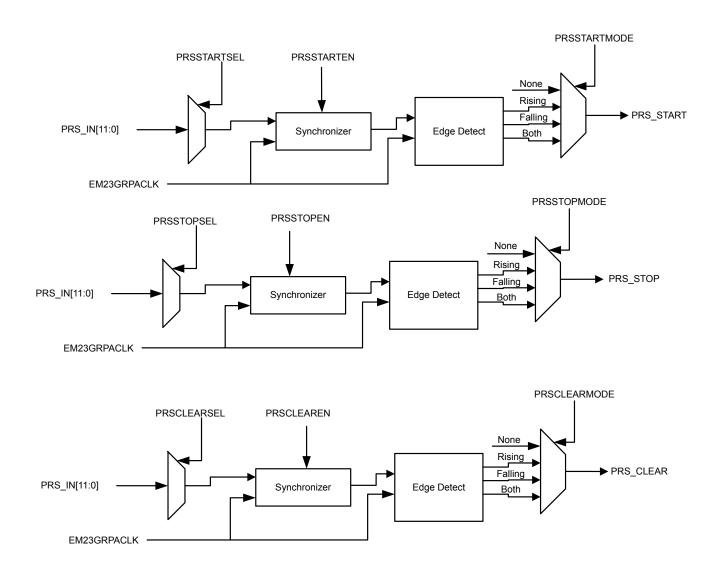

|     | 18.5 PRS Input Triggers                                            |            |

|     | 18.6 Debug                                                         | 410        |

|     | 18.7 Output Action                                                 | . 411      |

|     | 18.8 PRS Output                                                    | 411        |

|     | 18.9 Interrupts                                                    | 411        |

|     | 18.10 Using the LETIMER in EM3.................................... | 411        |

|     | 18.11 Register access                                              | 411        |

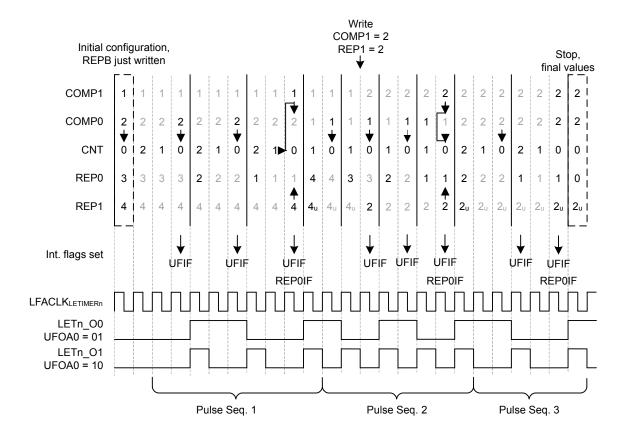

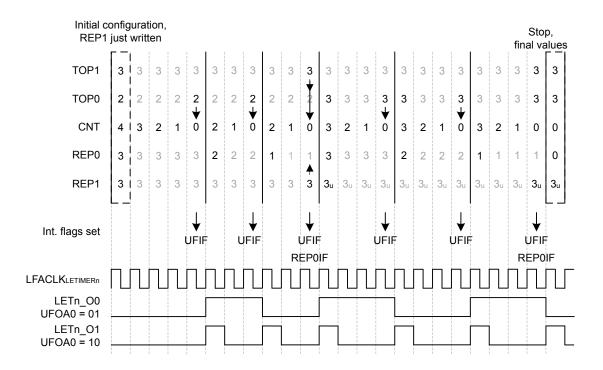

|     | 18.12 Programmer's Model                                           | . 412      |

|     | 18.12.1 FREE Running Mode                                          |            |

|     | 18.12.2 One Shot Mode                                              |            |

|     | 18.12.3 DOUBLE Mode                                                | 414        |

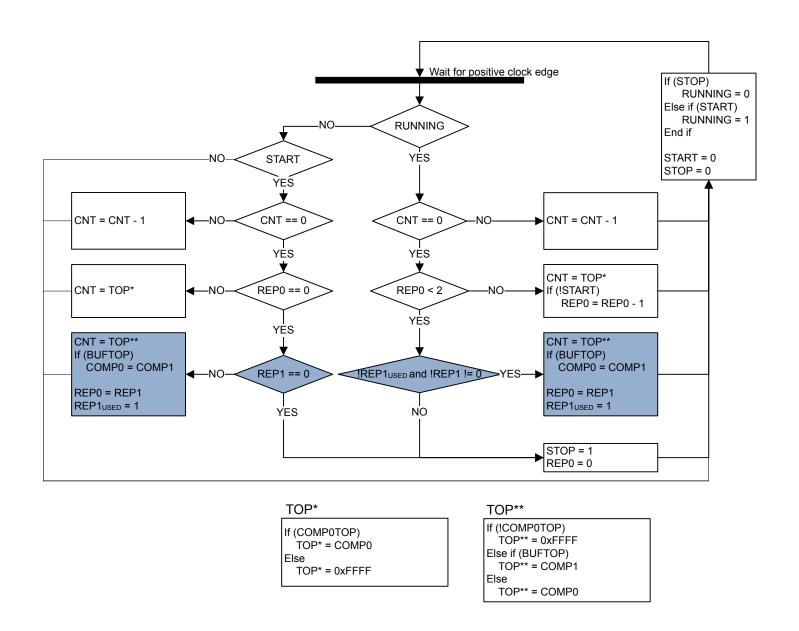

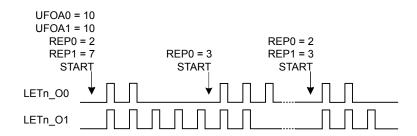

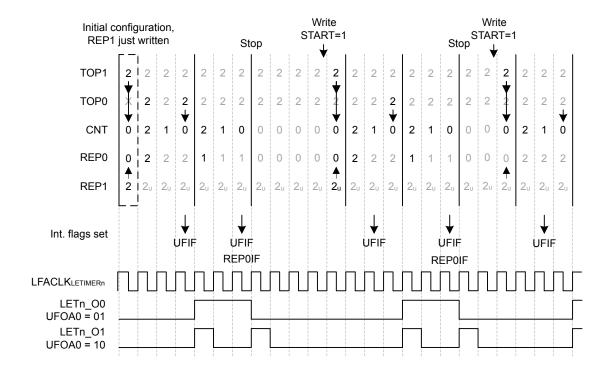

|     | 18.12.4 BUFFERED Mode                                              |            |

|     | 18.12.6 PWM Output                                                 |            |

|     | 18.13 Register Map                                                 |            |

|     | 18.14 Register Description                                         |            |

|     | 18.14.1 LETIMER_IPVERSION - IP version                             |            |

|     | 18.14.2 LETIMER_EN - module en                                     | 420        |

|     | 18.14.3 LETIMER_CTRL - Control Register                            | 421        |

|     | 18.14.4 LETIMER_CMD - Command Register                             | . 423      |

|     | 18.14.5 LETIMER_STATUS - Status Register                           | . 424      |

|     | 18.14.6 LETIMER_CNT - Counter Value Register                       |            |

|     | 18.14.7 LETIMER_COMP0 - Compare Value Register 0                   |            |

|     | 18.14.8 LETIMER_COMP1 - Compare Value Register 1                   |            |

|     | 18.14.9 LETIMER_TOP - Counter TOP Value Register                   |            |

|     | 18.14.10 LETIMER_TOPBUFF - Buffered Counter TOP Value              |            |

|     | 18.14.11 LETIMER_REP0 - Repeat Counter Register 0                  | 427<br>427 |

|     | IO 14 IZ LE UNIEK KERT - KROPALLOUNIPEKRONSIRET                    | 4//        |

| 18.14.13 LETIMER_IF - Interrupt Flag Register                       | . 428       |

|---------------------------------------------------------------------|-------------|

| 18.14.14 LETIMER_IEN - Interrupt Enable Register                    | . 429       |

| 18.14.15 LETIMER_SYNCBUSY - Synchronization Busy Register           |             |

| 18.14.16 LETIMER_PRSMODE - PRS Input mode select Register           | . 431       |

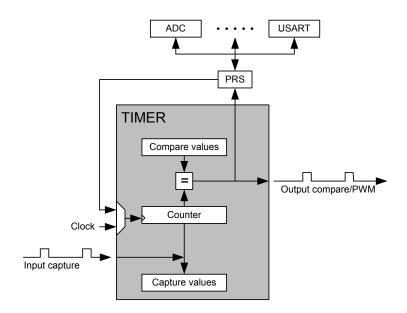

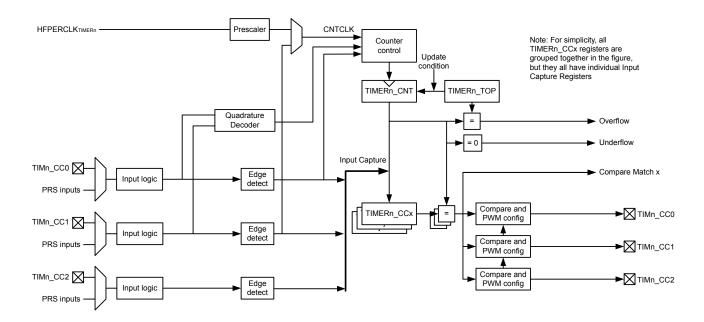

| 19. TIMER - Timer/Counter                                           | <i>A</i> 33 |

| 19.1 Introduction                                                   | . 433       |

| 19.2 Features                                                       | . 434       |

| 19.3 Functional Description                                         |             |

| 19.3.1 Register Access                                              |             |

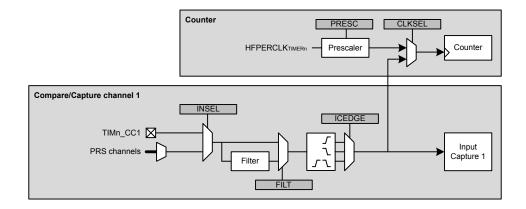

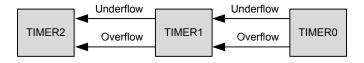

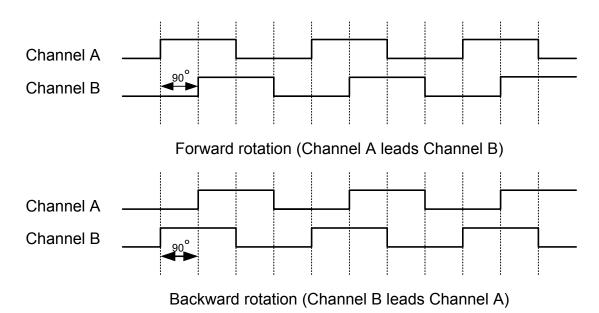

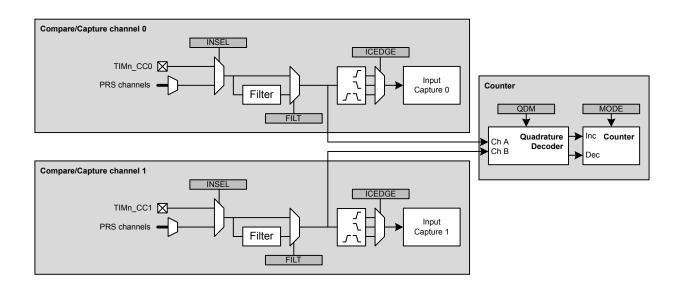

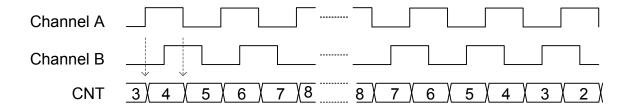

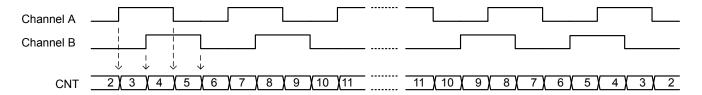

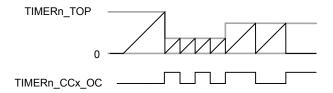

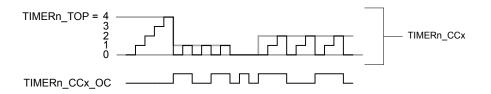

| 19.3.2 Counter Modes                                                |             |

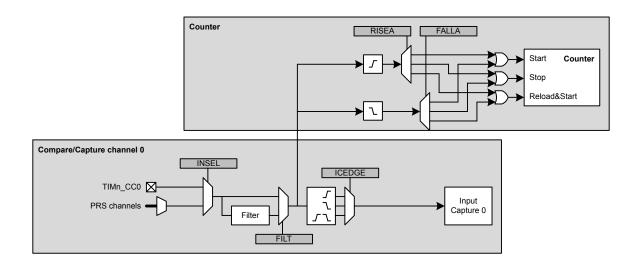

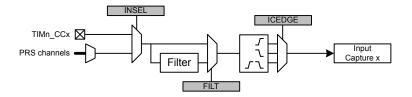

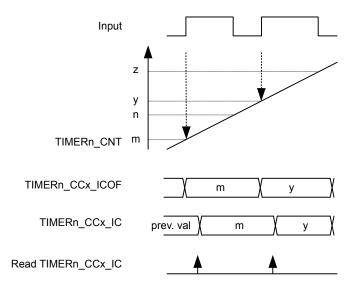

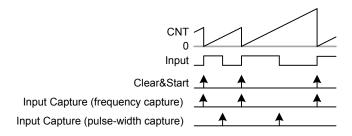

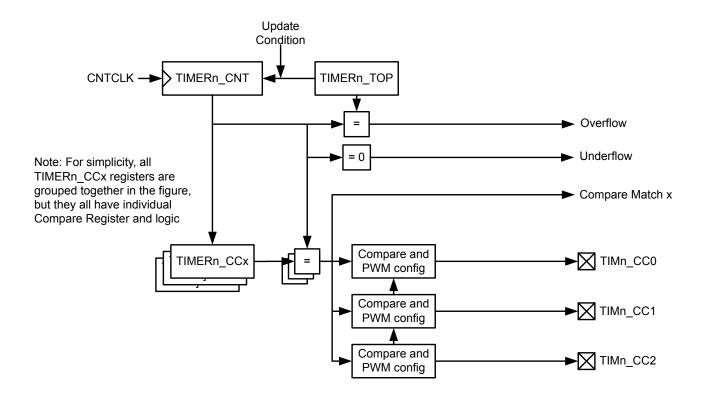

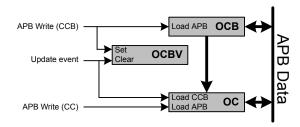

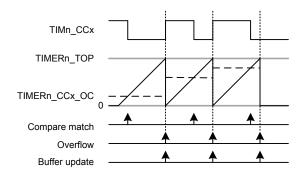

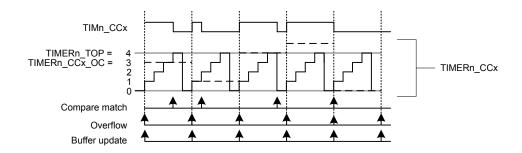

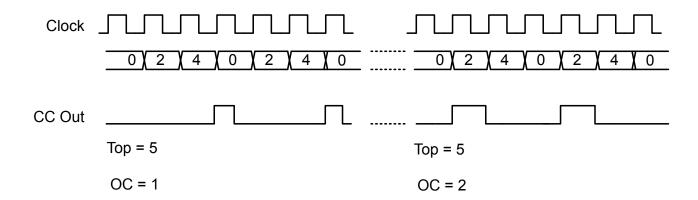

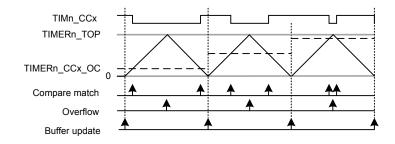

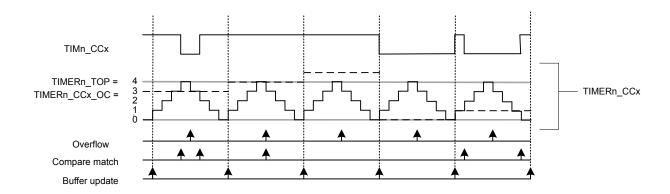

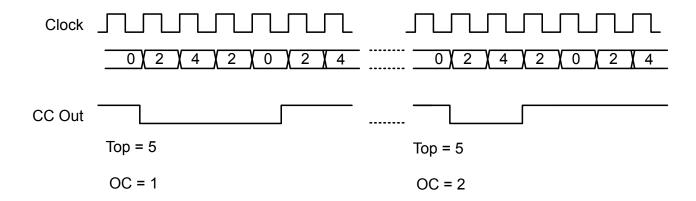

| 19.3.3 Compare/Capture Channels                                     |             |

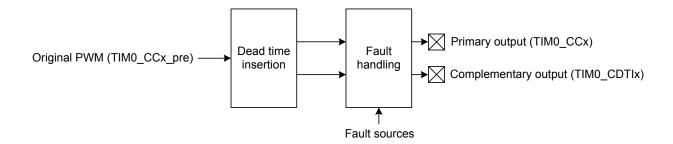

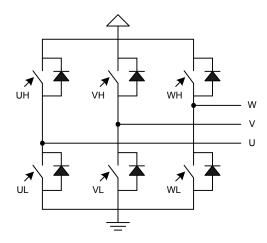

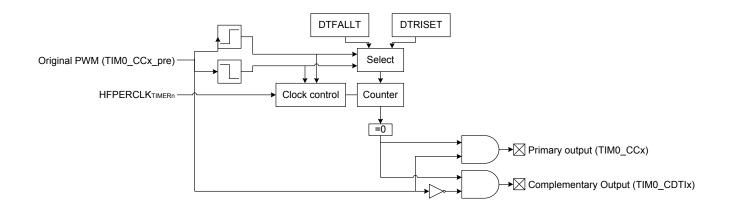

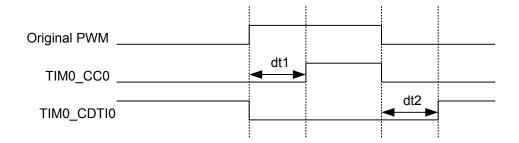

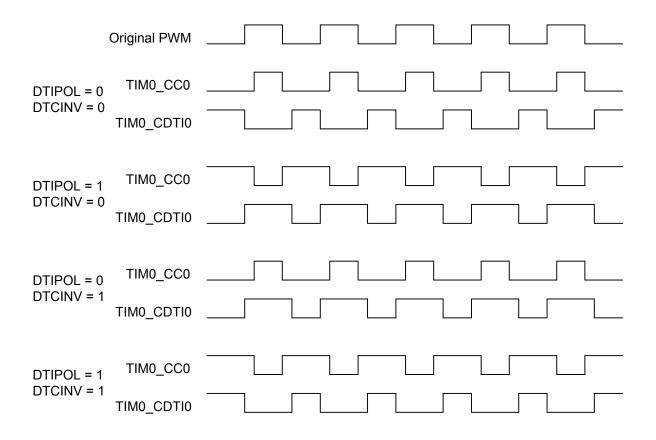

| 19.3.4 Dead-Time Insertion Unit                                     |             |

| 19.3.5 Debug Mode                                                   |             |

| 19.3.6 Interrupts, DMA and PRS Output                               |             |

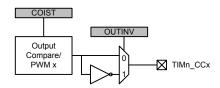

| 19.3.7 GPIO Input/Output                                            |             |

| 19.4 Register Map                                                   |             |

| 19.5 Register Description                                           |             |

| 19.5.1 TIMER_IFVERSION - IP VEISION ID                              |             |

| 19.5.3 TIMER CTRL - Control Register                                |             |

| 19.5.4 TIMER_CMD - Command Register                                 |             |

| 19.5.5 TIMER_STATUS - Status Register                               |             |

| 19.5.6 TIMER IF - Interrupt Flag Register                           |             |

| 19.5.7 TIMER_IEN - Interrupt Enable Register                        |             |

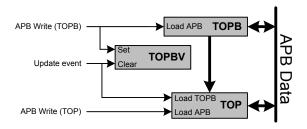

| 19.5.8 TIMER_TOP - Counter Top Value Register                       |             |

| 19.5.9 TIMER_TOPB - Counter Top Value Buffer Register.              |             |

| 19.5.10 TIMER CNT - Counter Value Register                          |             |

| 19.5.11 TIMER_LOCK - TIMER Configuration Lock Register              | . 474       |

| 19.5.12 TIMER_EN - module en                                        |             |

| 19.5.13 TIMER_CCx_CFG - CC Channel Configuration Register           | . 476       |

| 19.5.14 TIMER_CCx_CTRL - CC Channel Control Register                | .478        |

| 19.5.15 TIMER_CCx_OC - OC Channel Value Register                    | . 479       |

| 19.5.16 TIMER_CCx_OCB - OC Channel Value Buffer Register            |             |

| 19.5.17 TIMER_CCx_ICF - IC Channel Value Register                   | . 480       |

| 19.5.18 TIMER_CCx_ICOF - IC Channel Value Overflow Register         |             |

| 19.5.19 TIMER_DTCFG - DTI Configuration Register                    |             |

| 19.5.20 TIMER_DTTIMECFG - DTI Time Configuration Register           |             |

| 19.5.21 TIMER_DTFCFG - DTI Fault Configuration Register             |             |

| 19.5.22 TIMER_DTCTRL - DTI Control Register                         |             |

| 19.5.23 TIMER_DTOGEN - DTI Output Generation Enable Register        |             |

| 19.5.24 TIMER_DTFAULT - DTI Fault Register                          |             |

| 19.5.25 TIMER_DTFAULTC - DTI Fault Clear Register                   |             |

| 19.5.26 TIMER_DTLOCK - DTI Configuration Lock Register              | . 488       |

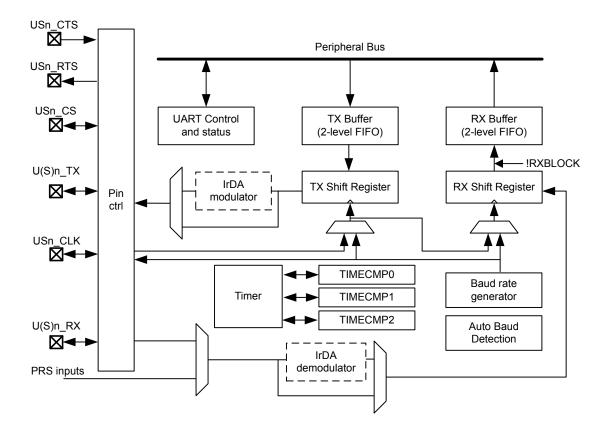

| 20. USART - Universal Synchronous Asynchronous Receiver/Transmitter | <i>4</i> 89 |

| 20.1 Introduction                                                   | 180         |

| 20.2 Features                                                     | . 490 |

|-------------------------------------------------------------------|-------|

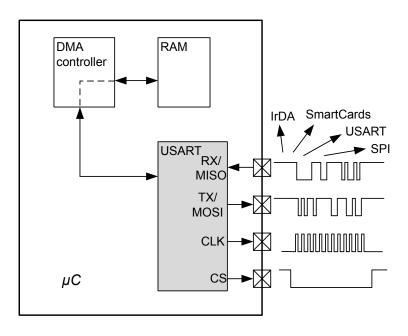

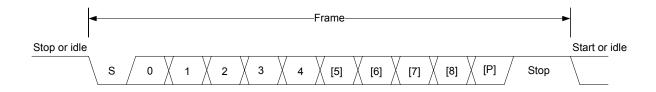

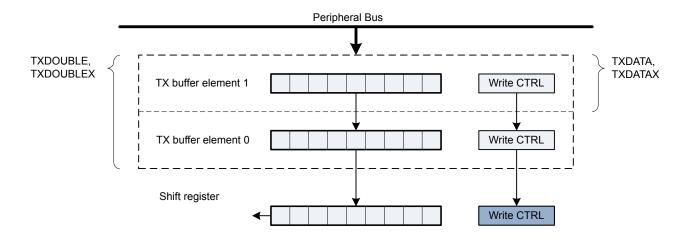

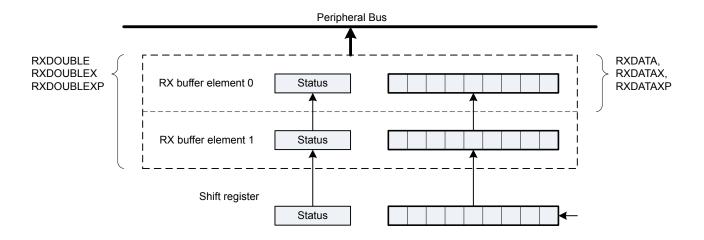

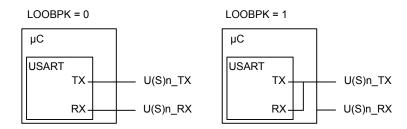

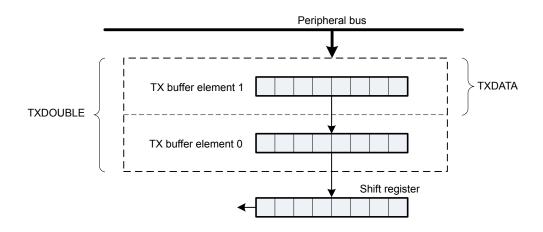

| 20.3 Functional Description                                       | . 491 |

| 20.3.1 Modes of Operation                                         | . 492 |

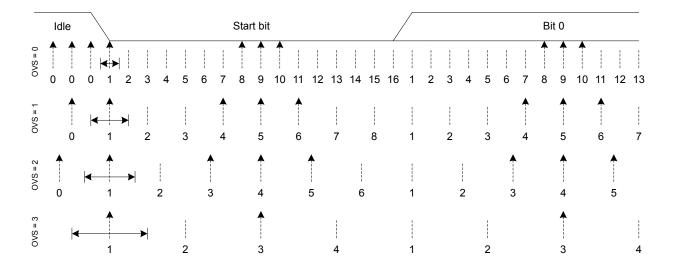

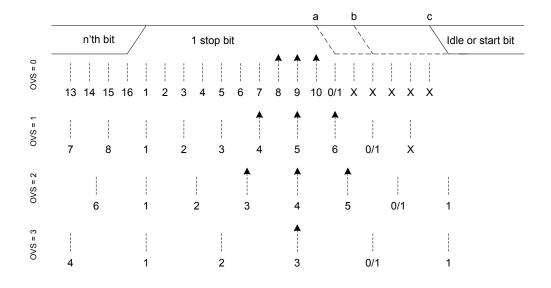

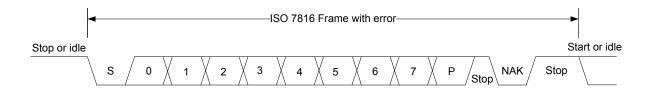

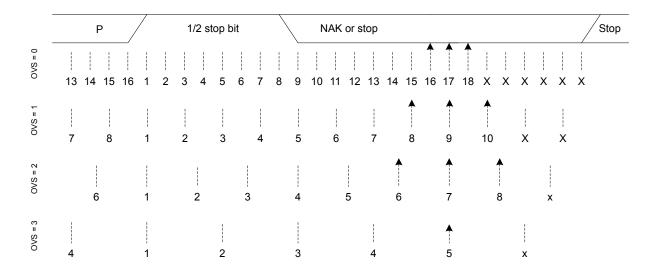

| 20.3.2 Asynchronous Operation                                     | . 492 |

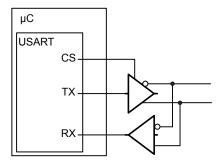

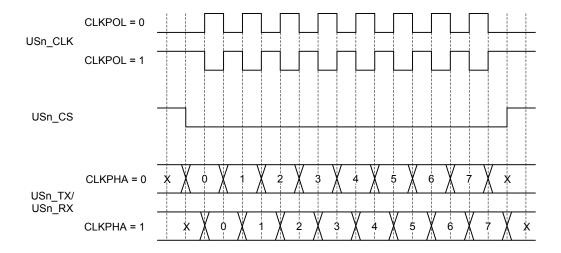

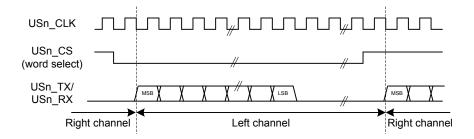

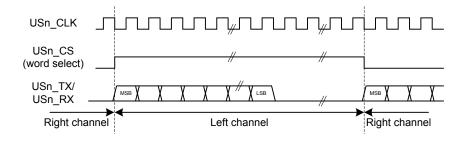

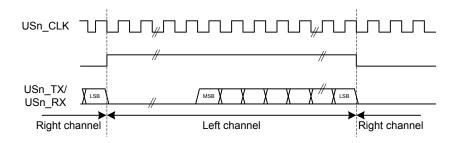

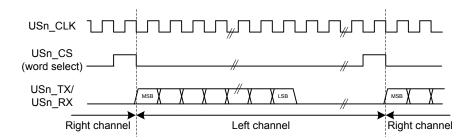

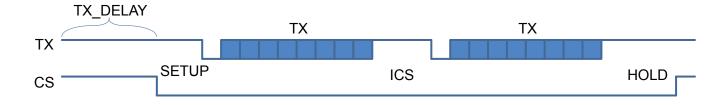

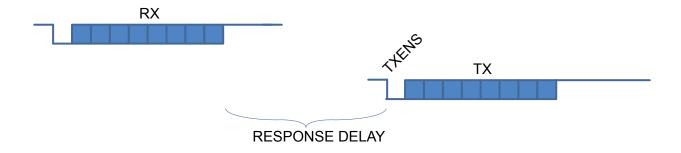

| 20.3.3 Synchronous Operation                                      | . 508 |

| 20.3.4 Hardware Flow Control                                      |       |

| 20.3.5 Debug Halt                                                 |       |

| 20.3.6 PRS-triggered Transmissions                                |       |

| 20.3.7 PRS RX Input                                               |       |

| 20.3.8 PRS CLK Input                                              |       |

| 20.3.9 DMA Support                                                |       |

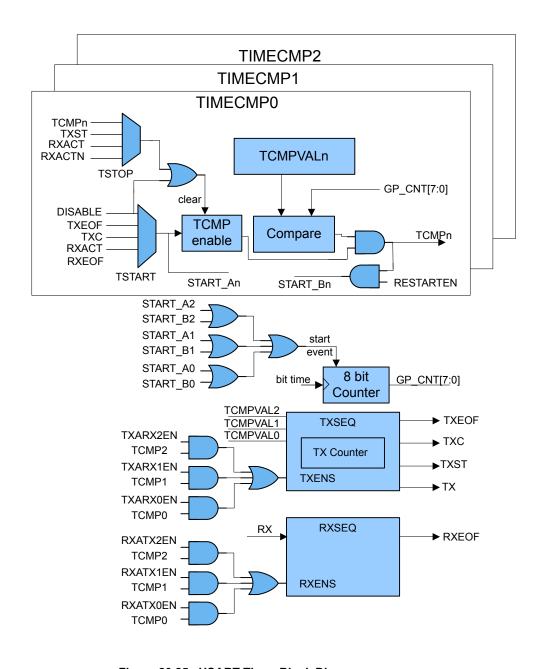

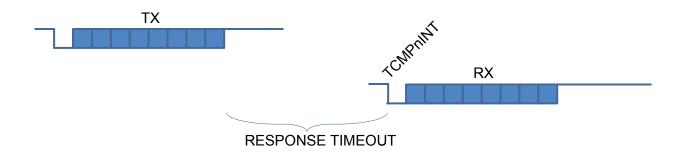

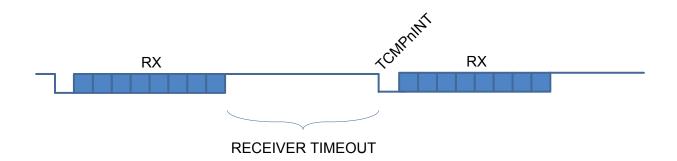

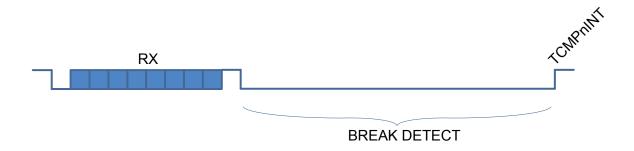

| 20.3.10 Timer                                                     |       |

| 20.3.11 Interrupts                                                |       |

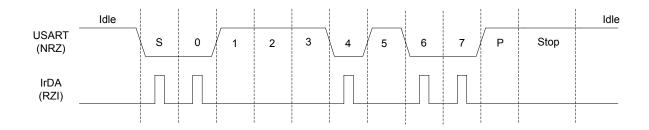

| 20.3.12 IrDA Modulator/ Demodulator                               |       |

|                                                                   |       |

| 20.4 Register Map                                                 |       |

| 20.5 Register Description                                         | . 526 |

| 20.5.1 USART_IPVERSION - IPVERSION                                | 526   |

| 20.5.2 USART_EN - USART Enable                                    | 526   |

| 20.5.3 USART_CTRL - Control Register                              |       |

| 20.5.4 USART_FRAME - USART Frame Format Register                  | . 532 |

| 20.5.5 USART_TRIGCTRL - USART Trigger Control register            |       |

| 20.5.6 USART_CMD - Command Register                               | 535   |

| 20.5.7 USART_STATUS - USART Status Register                       |       |

| 20.5.8 USART CLKDIV - Clock Control Register                      |       |

| 20.5.9 USART_RXDATAX - RX Buffer Data Extended Register           |       |

| 20.5.10 USART_RXDATA - RX Buffer Data Register                    |       |

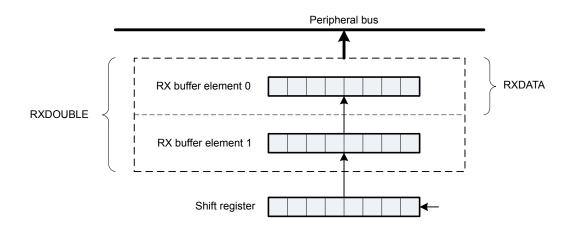

| 20.5.11 USART RXDOUBLEX - RX Buffer Double Data Extended Register |       |

| 20.5.12 USART RXDOUBLE - RX FIFO Double Data Register             |       |

| 20.5.13 USART_RXDATAXP - RX Buffer Data Extended Peek Register    |       |

| 20.5.14 USART_RXDOUBLEXP - RX Buffer Double Data Extended Peek R  |       |

| 20.5.15 USART_TXDATAX - TX Buffer Data Extended Register          |       |

| 20.5.16 USART_TXDATA - TX Buffer Data Register                    |       |

| 20.5.17 USART_TXDOUBLEX - TX Buffer Double Data Extended Register |       |

| 20.5.18 USART_TXDOUBLE - TX Buffer Double Data Register           |       |

| 20.5.19 USART_IF - Interrupt Flag Register.                       |       |

| 20.5.20 USART_IEN - Interrupt Enable Register                     |       |

| 20.5.21 USART_IRCTRL - IrDA Control Register                      |       |

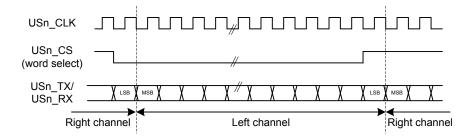

| 20.5.22 USART I2SCTRL - I/DA Control Register                     |       |

| _                                                                 |       |

| 20.5.23 USART_TIMING - Timing Register                            |       |

| 20.5.24 USART_CTRLX - Control Register Extended                   |       |

| 20.5.25 USART_TIMECMP0 - Used to generate interrupts and vario    |       |

| 20.5.26 USART_TIMECMP1 - Used to generate interrupts and vario    |       |

| 20.5.27 USART_TIMECMP2 - Used to generate interrupts and vario    | . 561 |

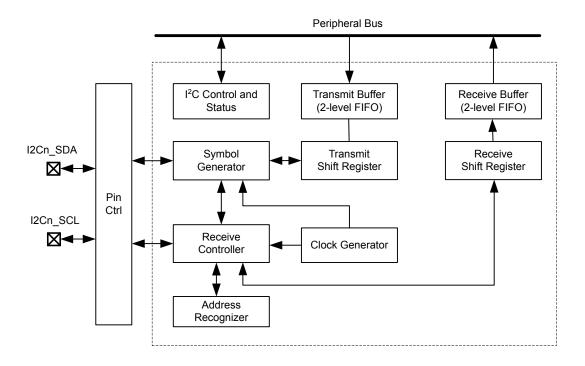

| 21. I2C - Inter-Integrated Circuit Interface                      | . 563 |

| 21.1 Introduction                                                 | . 563 |

| 21.2 Features                                                     | 563   |

| 21.3 Functional Description                                      | . 564 |

|------------------------------------------------------------------|-------|

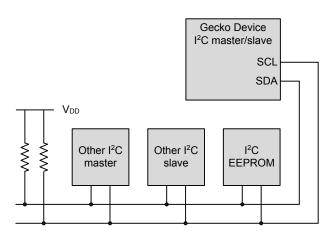

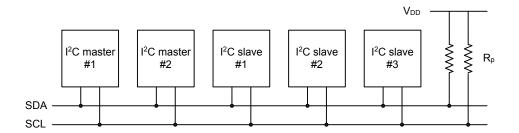

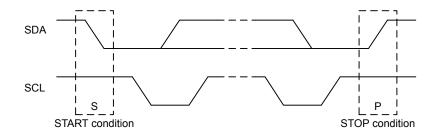

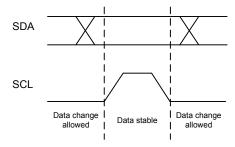

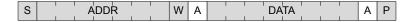

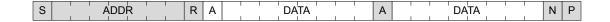

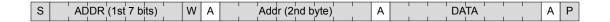

| 21.3.1 I2C-Bus Overview                                          | . 565 |

| 21.3.2 Enable and Reset                                          | . 569 |

| 21.3.3 Pin Configuration                                         | .569  |

| 21.3.4 Safely Disabling and Changing Slave Configuration         | . 569 |

| 21.3.5 Clock Generation                                          | .570  |

| 21.3.6 Arbitration                                               |       |

| 21.3.7 Buffers                                                   |       |

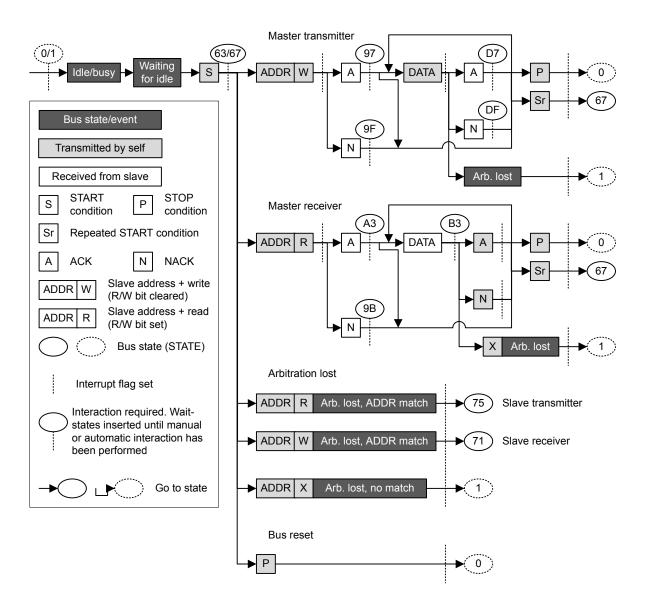

| 21.3.8 Master Operation                                          | .573  |

| 21.3.9 Bus States                                                |       |

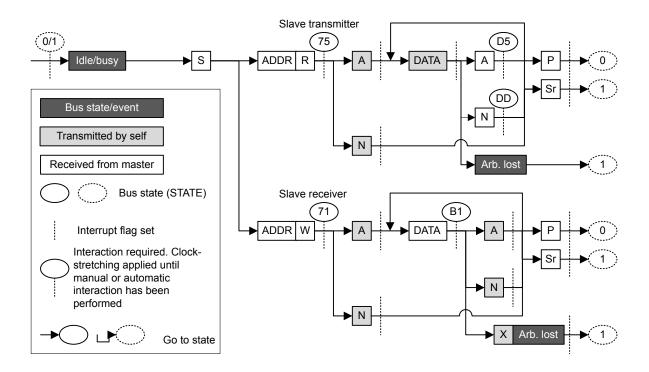

| 21.3.10 Slave Operation                                          | . 581 |

| 21.3.11 Transfer Automation                                      | . 585 |

| 21.3.12 Using 10-bit Addresses                                   |       |

| 21.3.13 Error Handling                                           |       |

| 21.3.14 DMA Support                                              |       |

| 21.3.15 Interrupts                                               |       |

| 21.3.16 Wake-up                                                  | . 588 |

| 21.4 Register Map                                                | . 589 |

| 21.5 Register Description                                        | . 591 |

| 21.5.1 I2C_IPVERSION - IP VERSION Register                       |       |

| 21.5.2 I2C_EN - Enable Register                                  | .591  |

| 21.5.3 I2C_CTRL - Control Register                               |       |

| 21.5.4 I2C_CMD - Command Register                                | 596   |

| 21.5.5 I2C_STATE - State Register                                | 597   |

| 21.5.6 I2C_STATUS - Status Register                              | 598   |

| 21.5.7 I2C_CLKDIV - Clock Division Register                      | . 599 |

| 21.5.8 I2C_SADDR - Slave Address Register                        | . 599 |

| 21.5.9 I2C_SADDRMASK - Slave Address Mask Register               | . 600 |

| 21.5.10 I2C_RXDATA - Receive Buffer Data Register                | .600  |

| 21.5.11 I2C_RXDOUBLE - Receive Buffer Double Data Register       | 601   |

| 21.5.12 I2C_RXDATAP - Receive Buffer Data Peek Register          | . 601 |

| 21.5.13 I2C_RXDOUBLEP - Receive Buffer Double Data Peek Register | . 602 |

| 21.5.14 I2C_TXDATA - Transmit Buffer Data Register               | .602  |

| 21.5.15 I2C_TXDOUBLE - Transmit Buffer Double Data Register      | .603  |

| 21.5.16 I2C_IF - Interrupt Flag Register                         | . 604 |

| 21.5.17 I2C_IEN - Interrupt Enable Register                      | 606   |

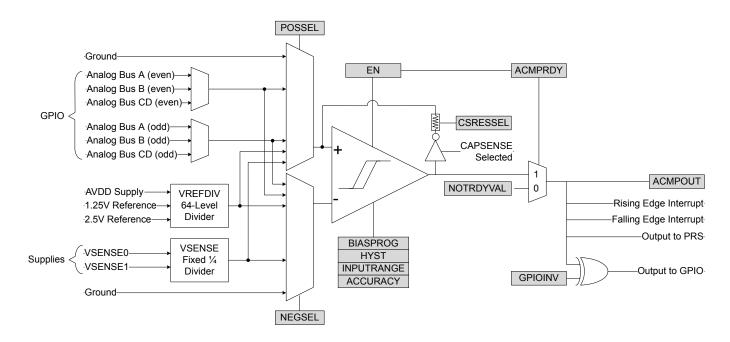

| 22. ACMP - Analog Comparator                                     | 608   |

| 22.1 Introduction                                                | 608   |

| 22.2 Features                                                    | . 608 |

| 22.3 Functional Description                                      | . 609 |

| 22.3.1 Configuration and Control                                 | 609   |

| 22.3.2 Warmup Time                                               |       |

| 22.3.3 Response Time                                             |       |

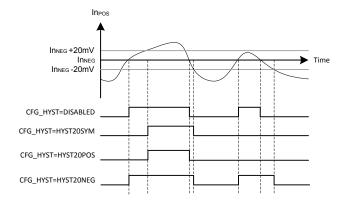

| 22.3.4 Hysteresis                                                | . 610 |

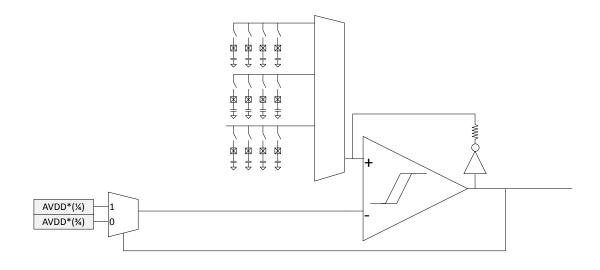

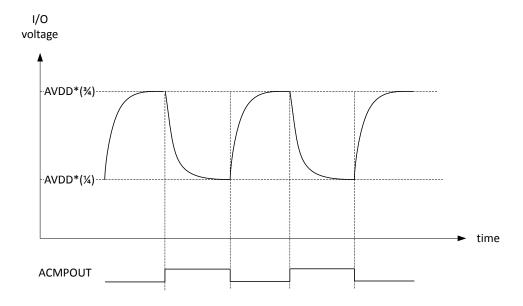

| 22.3.5 VREFDIV Sources                                           | . 611 |

| 22.3.6 Supply Voltage Monitoring (VSENSE)                        | .611  |

| 22.3.7 Input Range and Accuracy Settings                 | . 611 |

|----------------------------------------------------------|-------|

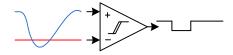

| 22.3.8 Capacitive Sense Mode                             | . 612 |

| 22.3.9 Interrupts and PRS Output                         | . 613 |

| 22.3.10 Output to GPIO                                   | . 613 |

| 22.4 Register Map                                        | . 614 |

| 22.5 Register Description                                | . 615 |

| 22.5.1 ACMP IPVERSION - IP version ID                    |       |

| 22.5.2 ACMP EN - ACMP enable                             |       |

| 22.5.3 ACMP_CFG - Configuration register                 |       |

| 22.5.4 ACMP CTRL - Control Register                      |       |

| 22.5.5 ACMP_INPUTCTRL - Input Control Register           |       |

| 22.5.6 ACMP_STATUS - Status Register                     |       |

| 22.5.7 ACMP_IF - Interrupt Flag Register                 |       |

| 22.5.8 ACMP_IEN - Interrupt Enable Register              | . 625 |

| 22.5.9 ACMP_SYNCBUSY - Syncbusy                          | 625   |

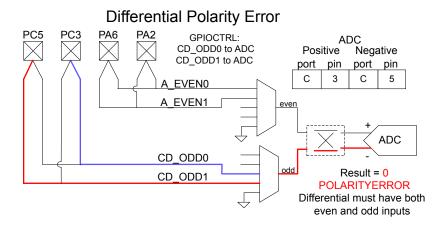

| 23. IADC - Incremental Analog to Digital Converter       | 626   |

| 23.1 Introduction                                        |       |

| 23.2 Features                                            |       |

|                                                          |       |

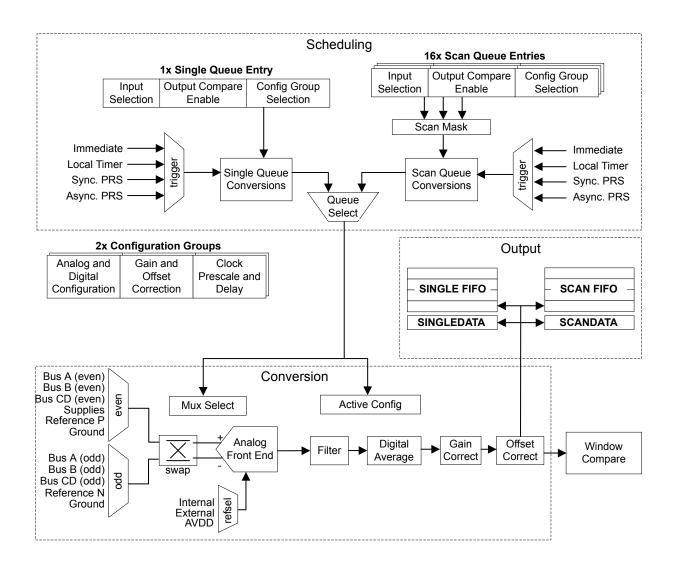

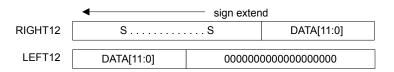

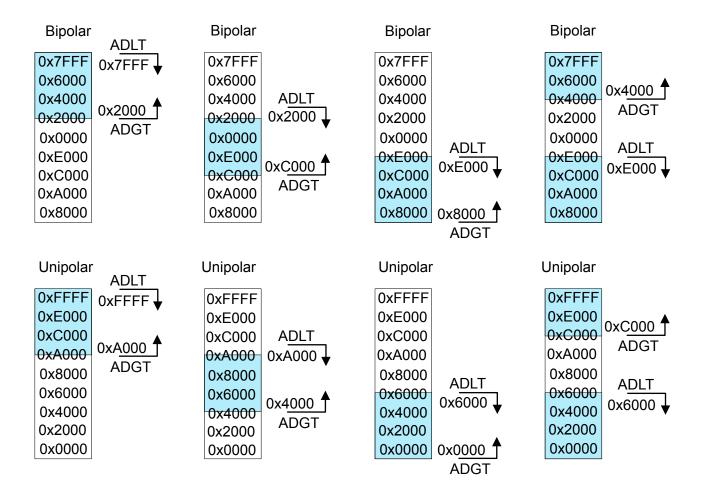

| 23.3 Functional Description                              |       |

| 23.3.1 Register Access                                   |       |

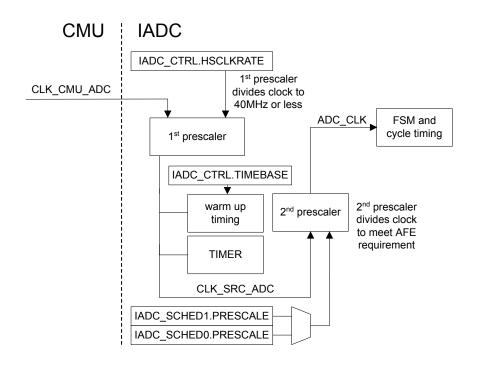

| 23.3.2 Clocking                                          |       |

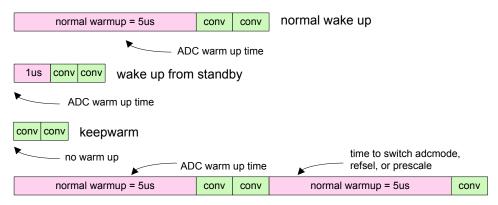

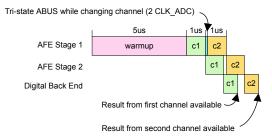

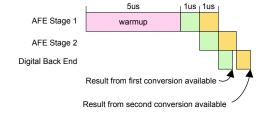

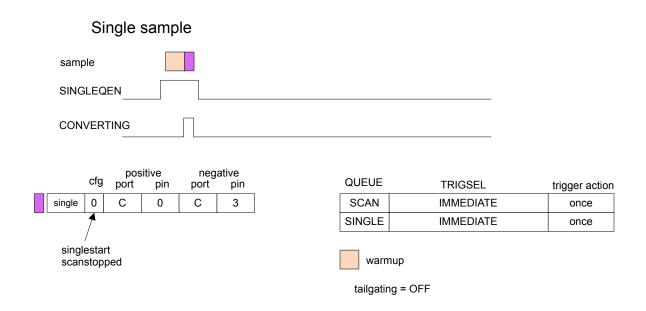

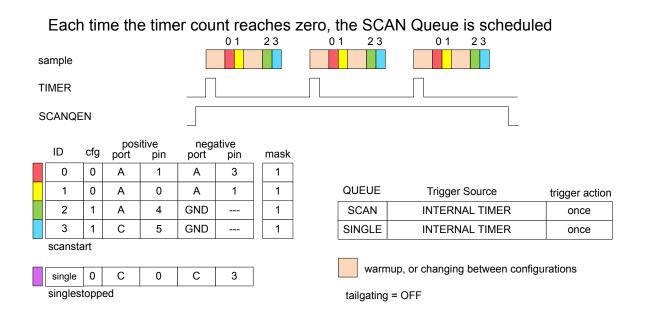

| 23.3.3 Conversion Timing                                 |       |

| 23.3.4 Reference Selection and Analog Gain               |       |

| 23.3.5 Input and Configuration Selection                 |       |

| 23.3.7 Output Data FIFOs                                 |       |

| 23.3.8 Window Compare                                    |       |

| 23.3.9 Interrupts                                        |       |

| 23.4 Register Map                                        |       |

| 23.5 Register Description                                |       |

| 23.5.1 IADC_IPVERSION - IPVERSION                        |       |

| 23.5.2 IADC_EN - Enable                                  |       |

| 23.5.3 IADC_CTRL - Control                               |       |

| 23.5.4 IADC_CMD - Command                                |       |

| 23.5.5 IADC_TIMER - Timer                                |       |

| 23.5.6 IADC_STATUS - Status                              |       |

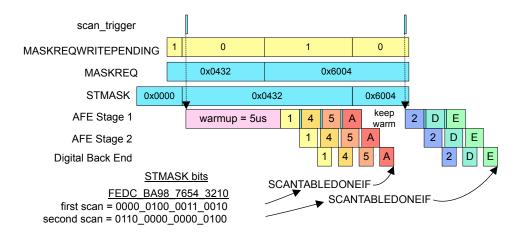

| 23.5.7 IADC_MASKREQ - Mask Request                       |       |

| 23.5.8 IADC_STMASK - Scan Table Mask                     |       |

| 23.5.9 IADC_CMPTHR - Digital Window Comparator Threshold |       |

| 23.5.10 IADC_IF - Interrupt Flags                        |       |

| 23.5.11 IADC_IEN - Interrupt Enable                      |       |

| 23.5.12 IADC_TRIGGER - Trigger                           |       |

| 23.5.13 IADC CFGx - Configuration                        |       |

| 23.5.14 IADC_SCALEx - Scaling                            |       |

| 23.5.15 IADC SCHEDx - Scheduling                         |       |

| 23.5.16 IADC SINGLEFIFOCFG - Single FIFO Configuration   |       |

| 23.5.17 IADC_SINGLEFIFODATA - Single FIFO Read Data | . 674 |

|-----------------------------------------------------|-------|

| 23.5.18 IADC_SINGLEFIFOSTAT - Single FIFO Status    | 674   |

| 23.5.19 IADC_SINGLEDATA - Single Data               | 675   |

| 23.5.20 IADC_SCANFIFOCFG - Scan FIFO Configuration  |       |

| 23.5.21 IADC_SCANFIFODATA - Scan FIFO Read Data     | .677  |

| 23.5.22 IADC_SCANFIFOSTAT - Scan FIFO Status        | 677   |

| 23.5.23 IADC_SCANDATA - Scan Data                   | 678   |

| 23.5.24 IADC_SINGLE - Single Queue Port Selection   | 679   |

| 23.5.25 IADC_SCANx - SCAN Entry                     | . 681 |

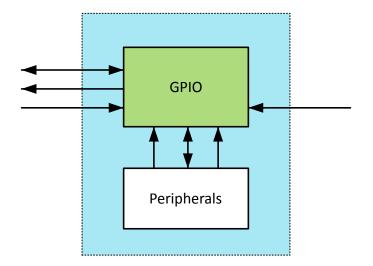

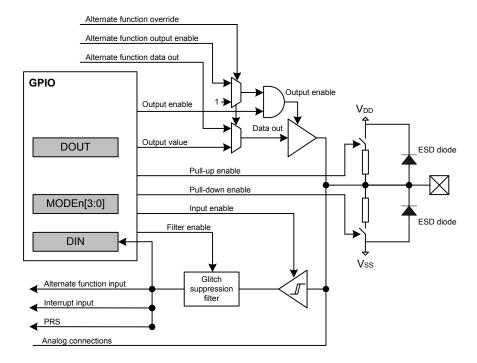

| 24. GPIO - General Purpose Input/Output             | 683   |

| 24.1 Introduction                                   |       |

|                                                     |       |

| 24.2 Features                                       |       |

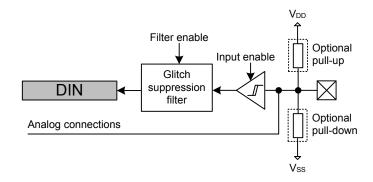

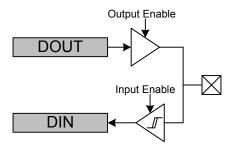

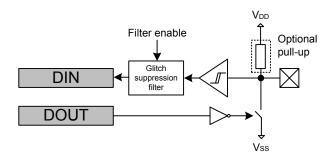

| 24.3 Functional Description                         | 685   |

| 24.3.1 Pin Configuration                            | .686  |

| 24.3.2 Alternate Port Control                       |       |

| 24.3.3 Slew Rate                                    |       |

| 24.3.4 Input Disable                                | 688   |

| 24.3.5 Configuration Lock                           | 688   |

| 24.3.6 EM2 Functionality                            |       |

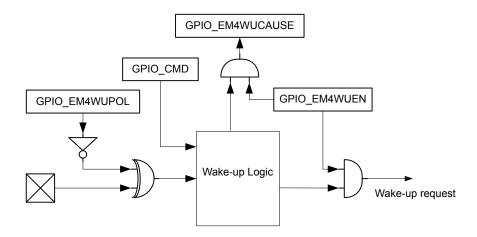

| 24.3.7 EM4 Functionality                            | . 688 |

| 24.3.8 EM4 Wakeup                                   |       |

| 24.3.9 Debug Connections                            | 689   |

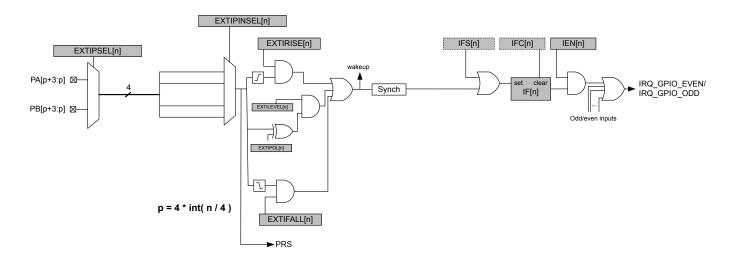

| 24.3.10 Interrupt Generation                        |       |

| 24.3.11 Output to PRS                               | 691   |

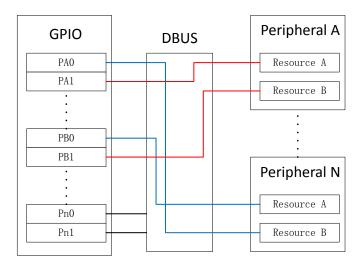

| 24.3.12 Peripheral Resource Routing                 | 691   |

| 24.4 Synchronization                                | .696  |

| 24.5 Register Map                                   | . 697 |

| 24.6 Register Description                           |       |

| 24.6.1 GPIO_PORTA_CTRL - Port control               |       |

| 24.6.2 GPIO PORTA MODEL - mode low                  |       |

| 24.6.3 GPIO_PORTA_DOUT - data out                   |       |

| 24.6.4 GPIO_PORTA_DIN - data in                     |       |

| 24.6.5 GPIO PORTB CTRL - Port control               |       |

| 24.6.6 GPIO_PORTB_MODEL - mode low                  |       |

| 24.6.7 GPIO PORTB DOUT - data out                   |       |

| 24.6.8 GPIO_PORTB_DIN - data in                     |       |

| 24.6.9 GPIO_PORTC_CTRL - Port control               |       |

| 24.6.10 GPIO PORTC MODEL - mode low                 |       |

| 24.6.11 GPIO_PORTC_DOUT - data out                  |       |

| 24.6.12 GPIO PORTC DIN - data in                    |       |

| 24.6.13 GPIO_PORTD_CTRL - Port control              |       |

| 24.6.14 GPIO PORTD MODEL - mode low                 |       |

| 24.6.15 GPIO_PORTD_DOUT - data out                  |       |

| 24.6.16 GPIO PORTD DIN - data in                    |       |

| 24.6.17 GPIO LOCK - main                            |       |

| =                                                   | 735   |

| 24.6.19 | GPIO_ABUSALLOC - A Bus allocation                    | 736   |

|---------|------------------------------------------------------|-------|

| 24.6.20 | GPIO_BBUSALLOC - B Bus allocation                    | 738   |

| 24.6.21 | GPIO_CDBUSALLOC - CD Bus allocation                  | .740  |

| 24.6.22 | GPIO_EXTIPSELL - External Interrupt Port Select Low  | 742   |

|         | GPIO_EXTIPINSELL - External Interrupt Pin Select Low | 745   |

|         | <del>-</del>                                         | .747  |

|         |                                                      | 748   |

|         | <del>-</del>                                         | 748   |

|         |                                                      | 749   |

|         |                                                      | . 749 |

|         | _                                                    | 750   |

|         | <del>-</del>                                         | .751  |

|         | _                                                    | 752   |

|         | GPIO ACMP0 ROUTEEN - ACMP0 pin enable                | 752   |

|         | ·                                                    | .753  |

|         | GPIO ACMP1 ROUTEEN - ACMP1 pin enable                | .753  |

|         | <u> </u>                                             | .754  |

|         |                                                      | .754  |

|         | GPIO CMU CLKIN0ROUTE - CLKIN0 port/pin select        | .755  |

|         | GPIO_CMU_CLKOUT0ROUTE - CLKOUT0 port/pin select      | 7.55  |

|         | GPIO CMU CLKOUT1ROUTE - CLKOUT1 port/pin select      | 7.56  |

|         | GPIO_CMU_CLKOUT2ROUTE - CLKOUT2 port/pin select      | 7.56  |

|         | GPIO_FRC_ROUTEEN - FRC pin enable                    | 757   |

|         | GPIO_FRC_DCLKROUTE - DCLK port/pin select            | 757   |

|         | GPIO_FRC_DFRAMEROUTE - DFRAME port/pin select        | 758   |

|         | GPIO_FRC_DOUTROUTE - DOUT port/pin select            | 758   |

|         | GPIO I2C0 ROUTEEN - I2C0 pin enable                  | 759   |

|         | = = ·                                                | 759   |

|         |                                                      | 760   |

|         | GPIO_I2C1_ROUTEEN - I2C1 pin enable                  | 760   |

|         | ;                                                    | 761   |

|         |                                                      |       |

|         | GPIO_I2C1_SDAROUTE - SDA port/pin select             |       |

|         | GPIO_LETIMERO_OUTOROUTE - OUT0 port/pin select       |       |

|         | GPIO LETIMERO OUT1ROUTE - OUT1 port/pin select       |       |

|         |                                                      |       |

|         | <u> </u>                                             |       |

|         |                                                      |       |

|         | — — — · · ·                                          |       |

|         | GPIO_MODEM_DCLKROUTE - DCLK port/pin select          |       |

|         | GPIO_MODEM_DINROUTE - DIN port/pin select            |       |

|         | GPIO_MODEM_DOUTROUTE - DOUT port/pin select          |       |

|         | GPIO_PRS0_ROUTEEN - PRS0 pin enable                  |       |

|         |                                                      | .768  |

|         |                                                      | .769  |

|         | GPIO_PRS0_ASYNCH2ROUTE - ASYNCH2 port/pin select     |       |

|         |                                                      | .770  |

|         |                                                      | .770  |

| 74 h hh | GPIO_PRS0_ASYNCH5ROUTE - ASYNCH5 port/pin select     | 771   |

| 24.6.67 | GPIO_PRS0_ASYNCH6ROUTE - ASYNCH6 port/pin select   | .771 |

|---------|----------------------------------------------------|------|

| 24.6.68 | GPIO_PRS0_ASYNCH7ROUTE - ASYNCH7 port/pin select   | .772 |

| 24.6.69 | GPIO_PRS0_ASYNCH8ROUTE - ASYNCH8 port/pin select   | .772 |

| 24.6.70 | GPIO_PRS0_ASYNCH9ROUTE - ASYNCH9 port/pin select   | .773 |

| 24.6.71 | GPIO_PRS0_ASYNCH10ROUTE - ASYNCH10 port/pin select | .773 |

|         | GPIO_PRS0_ASYNCH11ROUTE - ASYNCH11 port/pin select | .774 |

|         |                                                    | .774 |

|         |                                                    | .775 |

|         | GPIO_PRS0_SYNCH2ROUTE - SYNCH2 port/pin select     | .775 |

|         |                                                    | .776 |

|         |                                                    | 777  |

|         | GPIO_TIMER0_CC0ROUTE - CC0 port/pin select         | 7.78 |

|         | GPIO_TIMER0_CC1ROUTE - CC1 port/pin select         | 7.78 |

|         | GPIO_TIMER0_CC2ROUTE - CC2 port/pin select         | 7.79 |

|         | GPIO_TIMER0_CDTI0ROUTE - CDTI0 port/pin select     | .779 |

|         | <u> </u>                                           | .780 |

|         |                                                    | .780 |

|         | ' '                                                | 781  |

|         | GPIO_TIMER1_CC0ROUTE - CC0 port/pin select         | 7.82 |