For the information for microcontroller supports, see the following web site.

http://www.spansion.com/support/microcontrollers/

### **Preface**

Thank you for your continued use of Cypress products.

Read this manual and Data Sheet thoroughly before using products in this family.

### **Purpose of This Manual and Intended Readers**

This manual explains the functions and operations of this family and describes how it is used. The manual is intended for engineers engaged in the actual development of products using this family.

For the descriptions on Analog macro, Timer, and Communication Macro, see the respective separate peripheral manual.

#### Note:

This manual explains the configuration and operation of the peripheral functions, but does not cover the specifics of each device in the series.

Users should refer to the respective data sheets of devices for device-specific details.

### **Trademark**

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

### **Sample Programs and Development Environment**

Cypress offers sample programs free of charge for using the peripheral functions of the FM4 family. Cypress also makes available descriptions of the development environment required for this family. Feel free to use them to verify the operational specifications and usage of this Cypress microcontroller.

### **Microcontroller Support Information:**

http://www.spansion.com/support/microcontrollers/

### Note:

Note that the sample programs are subject to change without notice. Since they are offered as a

way to demonstrate standard operations and usage, evaluate them sufficiently before running them

on your system.

Cypress assumes no responsibility for any damage that may occur as a result of using a sample program.

### **Overall Organization of This Manual**

Peripheral Manual has 19 chapters and Appendixes as shown below.

CHAPTER 1: System Overview

CHAPTER 2-1: Clock

CHAPTER 2-2: Peripheral Clock Gating CHAPTER 2-3: High-Speed CR Trimming

on a TER 2 of Fight Opeca of Chillinning

CHAPTER 2-4: Low-Speed CR Prescaler

CHAPTER 3: Clock supervisor

**CHAPTER 4: Resets**

CHAPTER 5: Low-voltage Detection

CHAPTER 6: Low Power Consumption Mode

CHAPTER 7-1: VBAT Domain Configuration

CHAPTER 7-2: VBAT Domain (A)

CHAPTER 7-3: VBAT Domain (B)

**CHAPTER 8: Interrupts**

CHAPTER 9: External Interrupt and NMI Control Sections

CHAPTER 10: DMAC CHAPTER 11: DSTC CHAPTER 12: I/O Port

CHAPTER 13: CRC (Cyclic Redundancy Check)

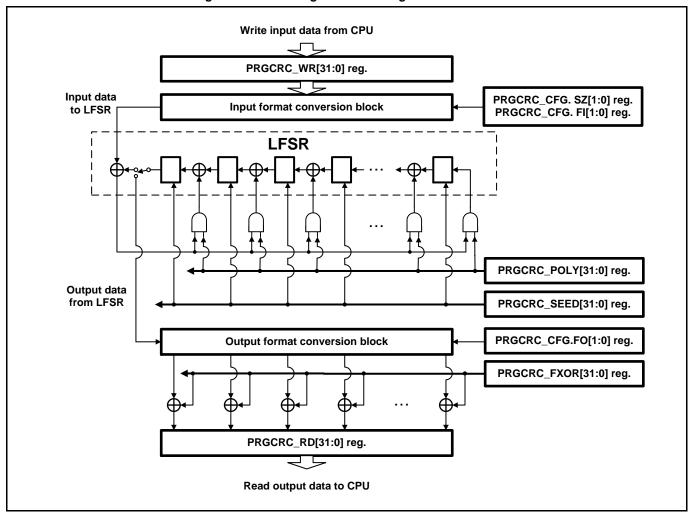

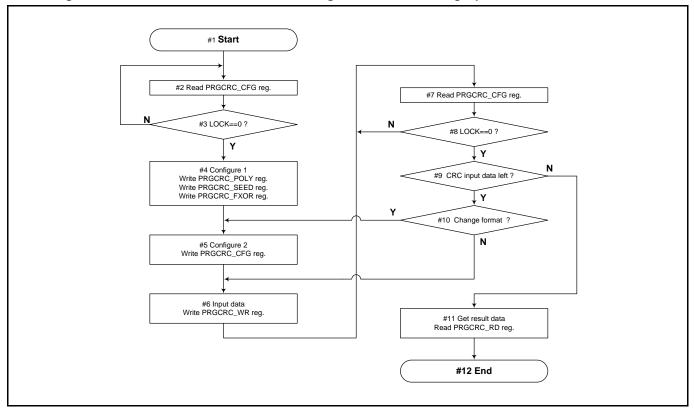

CHAPTER 14: External Bus Interface CHAPTER 15: SD Card Interface CHAPTER 16: Debug Interface CHAPTER 17: Flash Memory CHAPTER 18: Unique ID Register CHAPTER 19: Programmable CRC

**Appendixes**

## **Related Manuals**

The manuals related to this family are listed below. See the manual appropriate to the applicable conditions.

The contents of these manuals are subject to change without notice. Contact us to check the latest versions available.

### **Peripheral Manual**

- FM4 Family Peripheral Manual (this manual)

Called Peripheral Manual hereafter)

- FM4 Family Peripheral Manual Timer Part (MN709-00002)

Called Timer Part hereafter

- FM4 Family Peripheral Manual Analog Macro Part (MN709-00003)

Called Analog Macro Part hereafter

- FM4 Family Peripheral Manual Communication Macro Part (MN709-00004)

Called Communication Macro Part hereafter

- FM4 Family Peripheral Manual GDC Part (MN709-00014)

Called GDC Part hereafter

### **Data Sheet**

For details about device-specific, electrical characteristics, package dimensions, ordering information etc., see the following document.

■ 32-bit Microcontroller FM4 Family Data Sheet

### Note:

The data sheets for each series are provided.

See the appropriate data sheet for the series that you are using.

### **CPU Programming Manual**

For details about ARM Cortex-M4F core, see the following documents that can be obtained from http://www.arm.com/.

- Cortex-M4 Technical Reference Manual

- ARMv7-M Architecture Application Level Reference Manual

## **Flash Programming Manual**

For details about the functions and operations of the built-in flash memory, see the following document.

■ FM4 Family Flash Programming Manual

### Note:

Flash programming manuals for each series are provided.

See the appropriate flash programming manual for the series that you are using.

## **How to Use This Manual**

### **Finding a Function**

The following methods can be used to search for the explanation of a desired function in this manual:

■ Search from the table of the contents

The table of the contents lists the manual contents in the order of description.

■ Search from the register

The address where each register is located is not described in the text. To verify the address of a register, see A. Register Map in Appendixes.

## **About the Chapters**

Basically, this manual explains 1 peripheral function per chapter.

### **Terminology**

This manual uses the following terminology.

| Term      | Explanation                           |

|-----------|---------------------------------------|

| Word      | Indicates access in units of 32 bits. |

| Half word | Indicates access in units of 16 bits. |

| Byte      | Indicates access in units of 8 bits.  |

### **Notations**

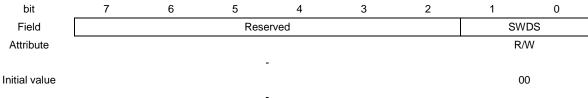

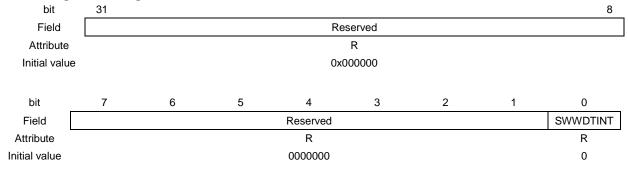

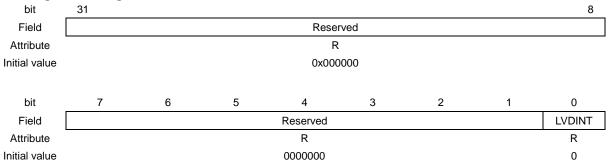

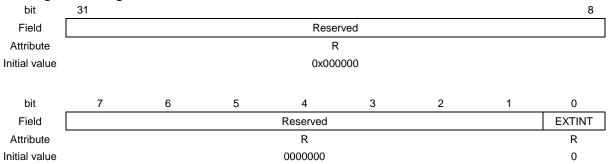

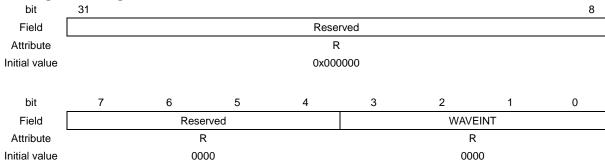

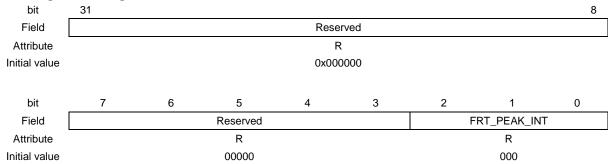

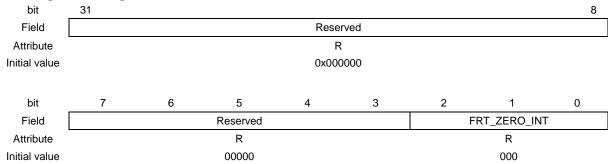

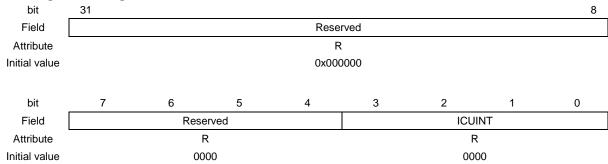

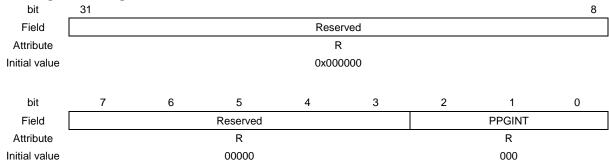

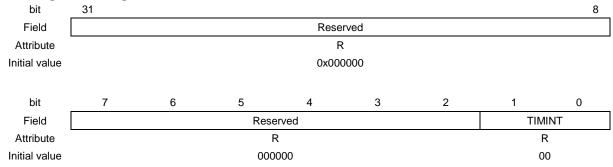

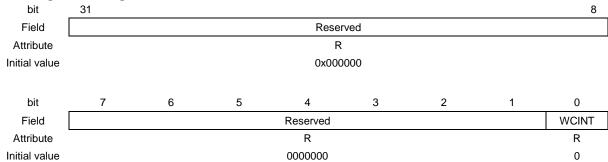

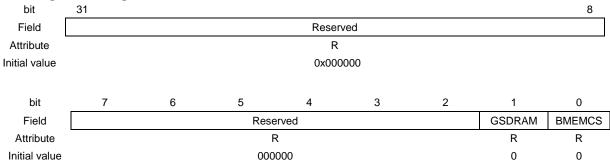

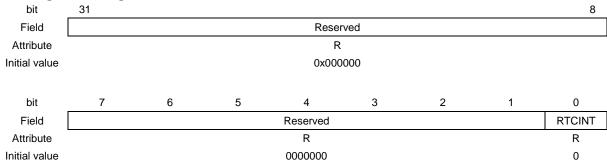

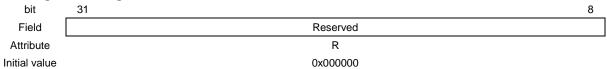

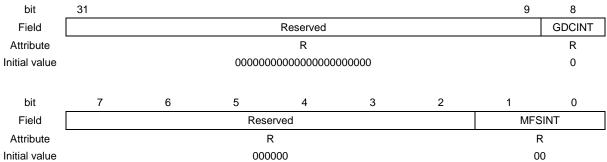

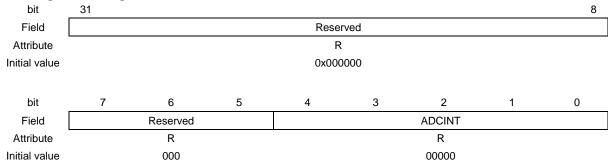

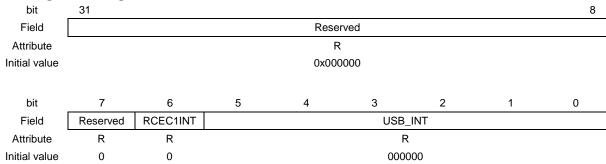

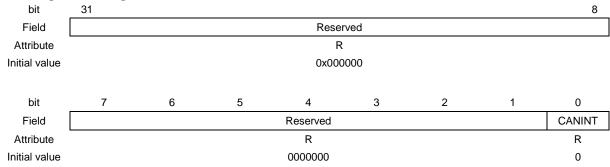

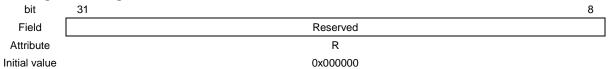

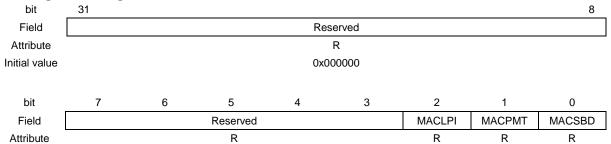

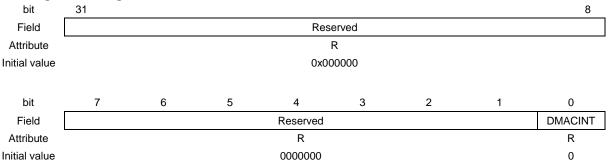

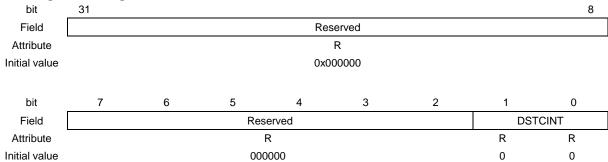

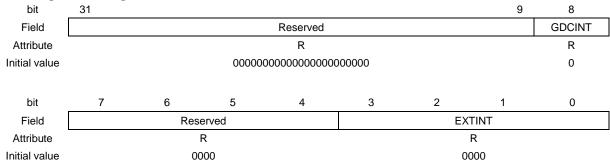

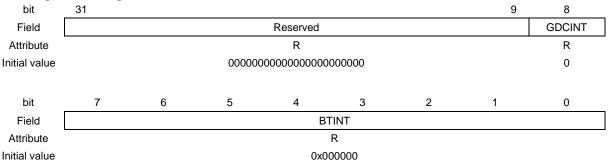

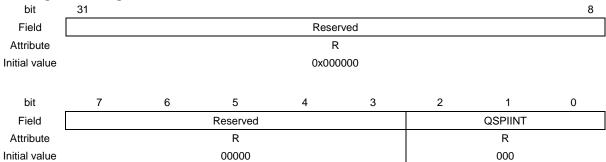

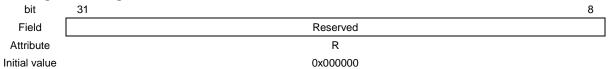

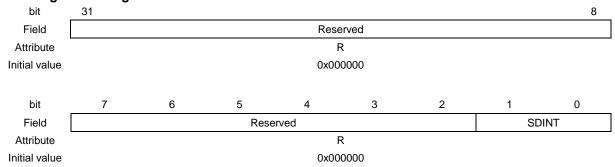

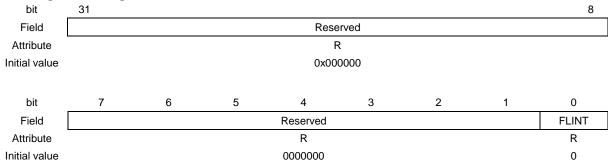

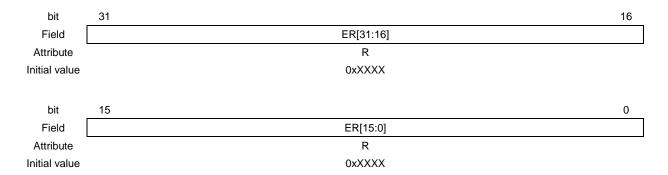

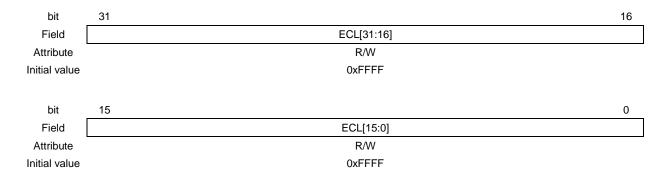

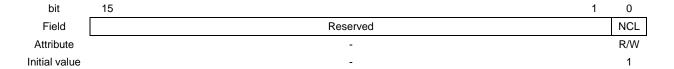

■ The notations in bit configuration of the register explanation of this manual are written as follows.

bit: bit numberField: bit field name

Attribute: Attributes for read and write of each bit

R: Read onlyW: Write only

R/W: Readable/Writable

- -: Undefined

Initial value: Initial value of the register after reset

0: Initial value is 01: Initial value is 1

X: Initial value is undefined

■ The multiple bits are written as follows in this manual.

Example: bit7:0 indicates the bits from bit7 to bit0

■ The values such as for addresses are written as follows in this manual.

Hexadecimal number: 0x is attached in the beginning of a value as a prefix

(example: 0xFFFF)

Binary number: 0b is attached in the beginning of a value as a prefix

(example: 0b1111)

Decimal number: Written using numbers only (example: 1000)

## The Target Products in This Manual

■ In this manual, the products are classified into the following groups and are described follows.

For the descriptions such as TYPE1-M4, see the relevant items of the target product in the list below.

**Table 1 TYPE1-M4 Product List**

| Description in |                                                   | Flash memory size                   |                                     |

|----------------|---------------------------------------------------|-------------------------------------|-------------------------------------|

| this manual    | 1024 Kbytes                                       | 768 Kbytes                          | 512 Kbytes                          |

|                | MB9BF568M<br>MB9BF568N<br>MB9BF568R<br>MB9BF568RF | MB9BF567M<br>MB9BF567N<br>MB9BF567R | MB9BF566M<br>MB9BF566N<br>MB9BF566R |

| TYPE1-M4       | MB9BF468M                                         | MB9BF467M                           | MB9BF466M                           |

|                | MB9BF468N                                         | MB9BF467N                           | MB9BF466N                           |

|                | MB9BF468R                                         | MB9BF467R                           | MB9BF466R                           |

|                | MB9BF368M                                         | MB9BF367M                           | MB9BF366M                           |

|                | MB9BF368N                                         | MB9BF367N                           | MB9BF366N                           |

|                | MB9BF368R                                         | MB9BF367R                           | MB9BF366R                           |

|                | MB9BF168M                                         | MB9BF167M                           | MB9BF166M                           |

|                | MB9BF168N                                         | MB9BF167N                           | MB9BF166N                           |

|                | MB9BF168R                                         | MB9BF167R                           | MB9BF166R                           |

Table 2 TYPE2-M4 Product List

| Description in |            | Flash memory size |            |

|----------------|------------|-------------------|------------|

| this manual    | 512 Kbytes | 384 Kbytes        | 256 Kbytes |

|                | MB9BF566K  | MB9BF565K         | MB9BF564K  |

|                | MB9BF566L  | MB9BF565L         | MB9BF564L  |

|                | MB9BF466K  | MB9BF465K         | MB9BF464K  |

| TYPE2-M4       | MB9BF466L  | MB9BF465L         | MB9BF464L  |

| 1 1 PEZ-IVI4   | MB9BF366K  | MB9BF365K         | MB9BF364K  |

|                | MB9BF366L  | MB9BF365L         | MB9BF364L  |

|                | MB9BF166K  | MB9BF165K         | MB9BF164K  |

|                | MB9BF166L  | MB9BF165L         | MB9BF164L  |

Table 3 TYPE3-M4 Product List

| Description       |                                                                                                                                                                                                                                    | Flash memory size                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  | No-Flash                                                             |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| in this<br>manual | 2 Mbytes                                                                                                                                                                                                                           | 1.5 Mbytes                                                                                                                                                                                                                         | 1 Mbytes                                                                                                                                                                                                                         | SRAM size<br>256 Kbytes                                              |

|                   | S6E2CCA L0AGL20 S6E2CCA LHAGL20 S6E2CCAJ0AGV20 S6E2CCAJHAGV20 S6E2CCAJHAGB10 S6E2CCAJHAGB10 S6E2CCAHOAGV20 S6E2CCAHHAGV20 S6E2CCAHGAGV20 S6E2CCAJGAGV20 S6E2CCAJGAGV10 S6E2CCAJGAGB10 S6E2CCAJGAGB10                               | S6E2CC9 L0AGL20<br>S6E2CC9 LHAGL20<br>S6E2CC9J0AGV20<br>S6E2CC9JHAGV20<br>S6E2CC9J0AGB10<br>S6E2CC9JHAGB10<br>S6E2CC9H0AGV20<br>S6E2CC9HHAGV20                                                                                     | S6E2CC8 L0AGL20<br>S6E2CC8 LHAGL20<br>S6E2CC8J0AGV20<br>S6E2CC8JHAGV20<br>S6E2CC8J0AGB10<br>S6E2CC8JHAGB10<br>S6E2CC8H0AGV20<br>S6E2CC8HHAGV20<br>S6E2CC8HHAGV20<br>S6E2CC8JGAGB10<br>S6E2CC8JFAGB10                             | -                                                                    |

|                   | \$6E2C5A L0AGL20<br>\$6E2C5AJ0AGV20<br>\$6E2C5AJ0AGB10<br>\$6E2C5AH0AGV20                                                                                                                                                          | S6E2C59 L0AGL20<br>S6E2C59J0AGV20<br>S6E2C59J0AGB10<br>S6E2C59H0AGV20                                                                                                                                                              | S6E2C58 L0AGL20<br>S6E2C58J0AGV20<br>S6E2C58J0AGB10<br>S6E2C58H0AGV20                                                                                                                                                            | -                                                                    |

| TYPE3-M4          | S6E2C4A L0AGL20<br>S6E2C4AJ0AGV20<br>S6E2C4AJ0AGB10<br>S6E2C4AH0AGV20                                                                                                                                                              | S6E2C49 L0AGL20<br>S6E2C49J0AGV20<br>S6E2C49J0AGB10<br>S6E2C49H0AGV20                                                                                                                                                              | \$6E2C48 L0AGL20<br>\$6E2C48J0AGV20<br>\$6E2C48J0AGB10<br>\$6E2C48H0AGV20                                                                                                                                                        | -                                                                    |

|                   | S6E2C3A L0AGL20<br>S6E2C3AJ0AGV20<br>S6E2C3AJ0AGB10<br>S6E2C3AH0AGV20                                                                                                                                                              | S6E2C39 L0AGL20<br>S6E2C39J0AGV20<br>S6E2C39J0AGB10<br>S6E2C39H0AGV20                                                                                                                                                              | S6E2C38 L0AGL20<br>S6E2C38J0AGV20<br>S6E2C38J0AGB10<br>S6E2C38H0AGV20                                                                                                                                                            | -                                                                    |

|                   | \$6E2C2A L0AGL20<br>\$6E2C2A LHAGL20<br>\$6E2C2AJ0AGV20<br>\$6E2C2AJ0AGB10<br>\$6E2C2AJ0AGB10<br>\$6E2C2AJ0AGB10<br>\$6E2C2AJ0AGV20<br>\$6E2C2AH0AGV20<br>\$6E2C2AH0AGV20<br>\$6E2C1AL0AGL20<br>\$6E2C1AJ0AGV20<br>\$6E2C1AJ0AGV20 | \$6E2C29 L0AGL20<br>\$6E2C29 LHAGL20<br>\$6E2C29J0AGV20<br>\$6E2C29JHAGV20<br>\$6E2C29J0AGB10<br>\$6E2C29JHAGB10<br>\$6E2C29H0AGV20<br>\$6E2C29HHAGV20<br>\$6E2C29HHAGV20<br>\$6E2C19L0AGL20<br>\$6E2C19J0AGV20<br>\$6E2C19J0AGB10 | \$6E2C28L0AGL20<br>\$6E2C28LHAGL20<br>\$6E2C28J0AGV20<br>\$6E2C28JHAGV20<br>\$6E2C28JHAGB10<br>\$6E2C28JHAGB10<br>\$6E2C28H0AGV20<br>\$6E2C28H0AGV20<br>\$6E2C18L0AGL20<br>\$6E2C18J0AGV20<br>\$6E2C18J0AGB10<br>\$6E2C18J0AGB10 | S6E2C10H2AGV20<br>S6E2C10J2AGV20<br>S6E2C10J2AGB10<br>S6E2C10L2AGL20 |

## **Table 4 TYPE4-M4 Product List**

|                     | Flash memory    | size 384 Kbytes  |

|---------------------|-----------------|------------------|

| Description in this |                 | VRAM 512 Kbytes  |

| manual              | VRAM 512 Kbytes | +                |

|                     |                 | VFLASH 2 Mbytes  |

|                     | S6E2D35G0AGB30  |                  |

|                     | S6E2D35G0AGV20  | S6E2D35GJAMV20   |

|                     | S6E2D35G0AGE20  | S0E2D33GJAMV20   |

|                     | S6E2D35J0AGV20  |                  |

|                     | S6E2D55G0AGB30  |                  |

|                     | S6E2D55G0AGV20  | S6E2D55GJAMV20   |

|                     | S6E2D55G0AGE20  |                  |

| TVDE 4 M4           | S6E2D55J0AGV20  |                  |

| TYPE4-M4            | S6E2DF5G0AGB30  |                  |

|                     | S6E2DF5G0AGV20  | 00500550 1444/00 |

|                     | S6E2DF5G0AGE20  | S6E2DF5GJAMV20   |

|                     | S6E2DF5J0AGV20  |                  |

|                     | S6E2DH5G0AGB30  |                  |

|                     | S6E2DH5G0AGV20  | CCEODUEC IAMAYOO |

|                     | S6E2DH5G0AGE20  | S6E2DH5GJAMV20   |

|                     | S6E2DH5J0AGV20  |                  |

## **Table 5 TYPE5-M4 Product List**

| Description in | Flash me       | mory size      |

|----------------|----------------|----------------|

| this manual    | 1 Mbytes       | 512 Kbytes     |

|                | S6E2GM8JHAGV20 | S6E2GM6JHAGV20 |

|                | S6E2GM8J0AGV20 | S6E2GM6J0AGV20 |

|                | S6E2GM8HHAGV20 | S6E2GM6HHAGV20 |

|                | S6E2GM8H0AGV20 | S6E2GM6H0AGV20 |

|                | S6E2GK8JHAGV20 | S6E2GK6JHAGV20 |

|                | S6E2GK8J0AGV20 | S6E2GK6J0AGV20 |

|                | S6E2GK8HHAGV20 | S6E2GK6HHAGV20 |

| TYPE5-M4       | S6E2GK8H0AGV20 | S6E2GK6H0AGV20 |

| I YPE5-IVI4    | S6E2GH8J0AGV20 | S6E2GH6J0AGV20 |

|                | S6E2GH8H0AGV20 | S6E2GH6H0AGV20 |

|                | S6E2G28JHAGV20 | S6E2G26JHAGV20 |

|                | S6E2G28J0AGV20 | S6E2G26J0AGV20 |

|                | S6E2G28HHAGV20 | S6E2G26H0AGV20 |

|                | S6E2G28H0AGV20 | S6E2G26HHAGV20 |

|                | S6E2G38J0AGV20 | S6E2G36J0AGV20 |

| l              | S6E2G38H0AGV20 | S6E2G36H0AGV20 |

## **Table 6 TYPE6-M4 Product List**

| Description in | Flash me       | emory size     |

|----------------|----------------|----------------|

| this manual    | 512 Kbytes     | 256 Kbytes     |

|                | S6E2HG6G0AGV20 | S6E2HG4G0AGV20 |

|                | S6E2HG6F0AGV20 | S6E2HG4F0AGV20 |

|                | S6E2HG6E0AGV20 | S6E2HG4E0AGV20 |

|                | S6E2HG6G0AGB10 | S6E2HG4G0AGB10 |

|                | S6E2HE6G0AGV20 | S6E2HE4G0AGV20 |

|                | S6E2HE6F0AGV20 | S6E2HE4F0AGV20 |

|                | S6E2HE6E0AGV20 | S6E2HE4E0AGV20 |

| TYPE6-M4       | S6E2HE6G0AGB10 | S6E2HE4G0AGB10 |

| I I PEO-IVI4   | S6E2H46G0AGV20 | S6E2H44G0AGV20 |

|                | S6E2H46F0AGV20 | S6E2H44F0AGV20 |

|                | S6E2H46E0AGV20 | S6E2H44E0AGV20 |

|                | S6E2H46G0AGB10 | S6E2H44G0AGB10 |

|                | S6E2H16G0AGV20 | S6E2H14G0AGV20 |

|                | S6E2H16F0AGV20 | S6E2H14F0AGV20 |

|                | S6E2H16E0AGV20 | S6E2H14E0AGV20 |

|                | S6E2H16G0AGB10 | S6E2H14G0AGB10 |

# **Table of Contents**

| CHAPTER 1: System Overview                                         | 23    |

|--------------------------------------------------------------------|-------|

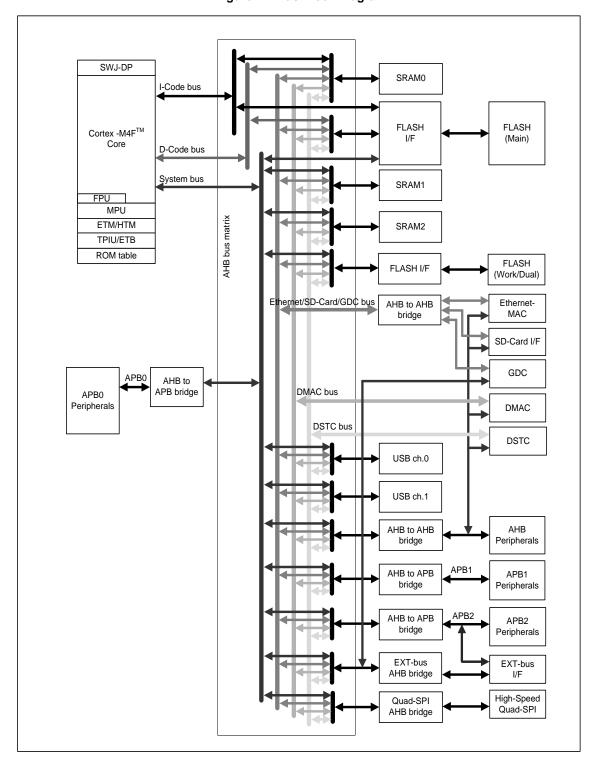

| 1. Bus Architecture                                                | 24    |

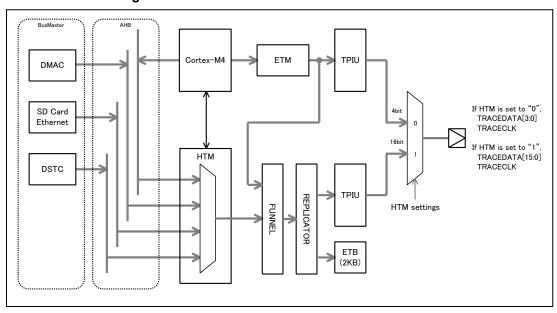

| 1.1. Bus Block Diagram                                             | 26    |

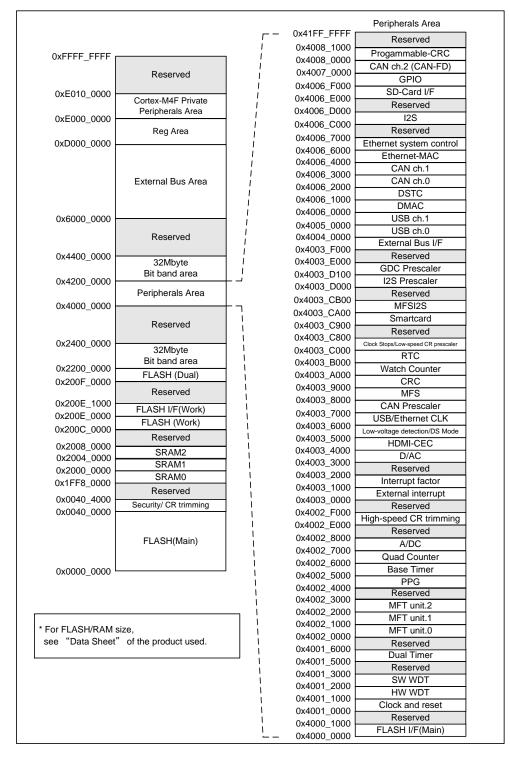

| 1.2. Memory Architecture                                           | 27    |

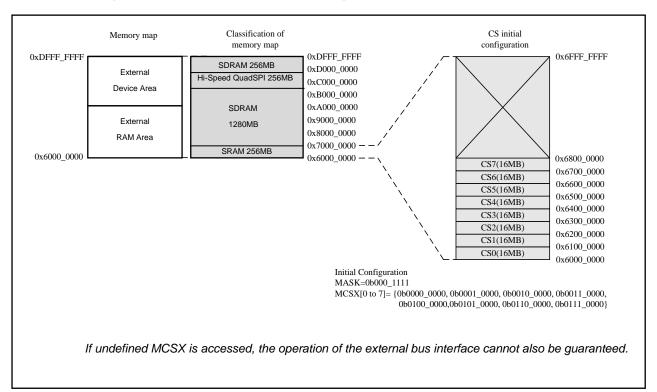

| 1.3. Memory Map                                                    | 28    |

| 1.4. Peripheral Address Map                                        |       |

| 2. Cortex-M4F Architecture                                         | 32    |

| 3. Mode                                                            | 35    |

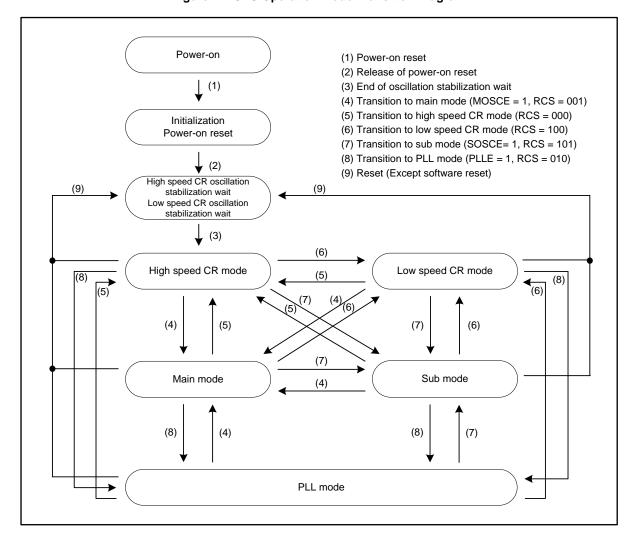

| CHAPTER 2-1: Clock                                                 | 37    |

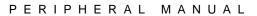

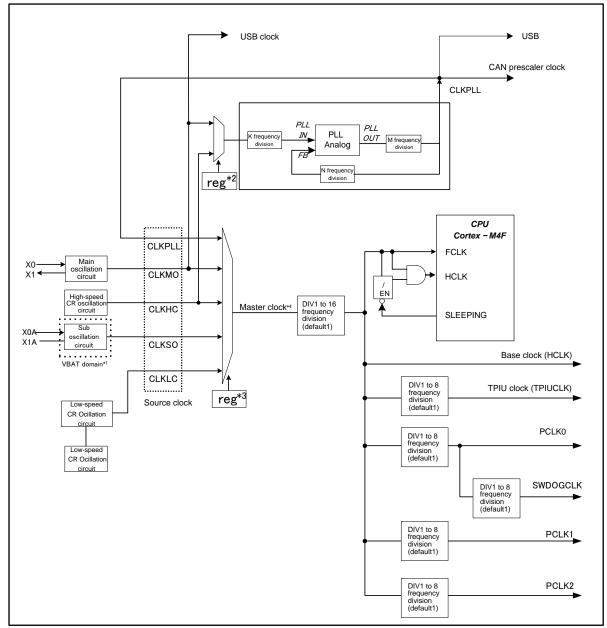

| 1. Clock Generation Unit Overview                                  | 38    |

| 2. Clock Generation Unit Configuration/Block Diagram               | 39    |

| 3. Clock Generation Unit Operations                                | 44    |

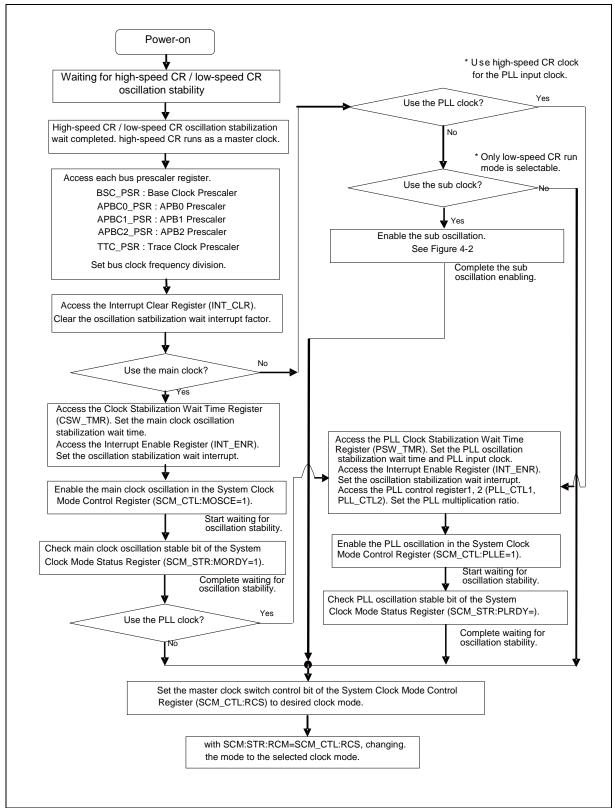

| 3.1. Selecting the clock mode                                      | 44    |

| 3.2. Internal bus clock frequency division control                 | 45    |

| 3.3. PLL clock control                                             | 46    |

| 3.4. Oscillation stabilization wait time                           | 48    |

| 3.5. Interrupt Factors                                             | 49    |

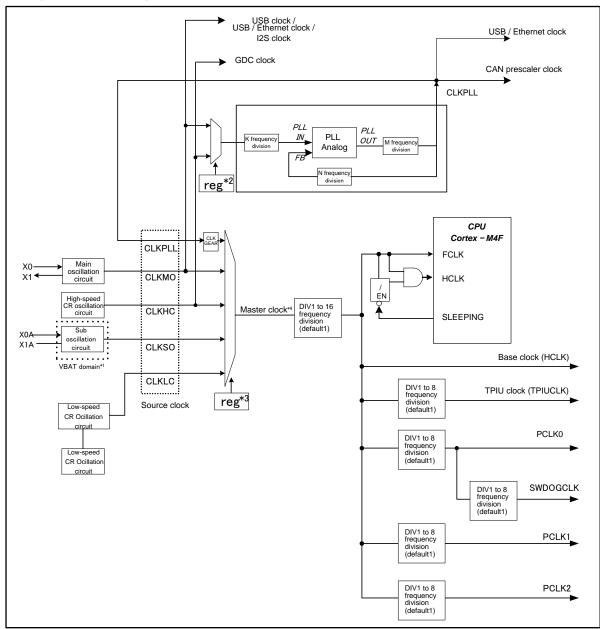

| 3.6. Clock Gear function                                           | 50    |

| 4. Clock Setup Procedure Examples                                  | 52    |

| 5. List of Clock Generation Unit Registers                         | 56    |

| 5.1. System Clock Mode Control Register (SCM_CTL)                  | 57    |

| 5.2. System Clock Mode Status Register (SCM_STR)                   | 59    |

| 5.3. Base Clock Prescaler Register (BSC_PSR)                       | 60    |

| 5.4. APB0 Prescaler Register (APBC0_PSR)                           | 61    |

| 5.5. APB1 Prescaler Register (APBC1_PSR)                           | 62    |

| 5.6. APB2 Prescaler Register (APBC2_PSR)                           | 63    |

| 5.7. Software Watchdog Clock Prescaler Register (SWC_PSR)          | 64    |

| 5.8. Trace Clock Prescaler Register (TTC_PSR)                      | 65    |

| 5.9. Clock Stabilization Wait Time Register (CSW_TMR)              | 66    |

| 5.10. PLL Clock Stabilization Wait Time Setup Register (PSW_TMR)   | 68    |

| 5.11. PLL Control Register 1 (PLL_CTL1)                            | 69    |

| 5.12. PLL Control Register 2 (PLL_CTL2)                            | 70    |

| 5.13. Debug Break Watchdog Timer Control Register (DBWDT_CTL)      |       |

| 5.14. Interrupt Enable Register (INT_ENR)                          | 72    |

| 5.15. Interrupt Status Register (INT_STR)                          | 73    |

| 5.16. Interrupt Clear Register (INT_CLR)                           | 74    |

| 5.17. PLL Clock Gear Control Register (PLLCG_CTL)                  | 76    |

| 6. Clock Generation Unit Usage Precautions                         | 78    |

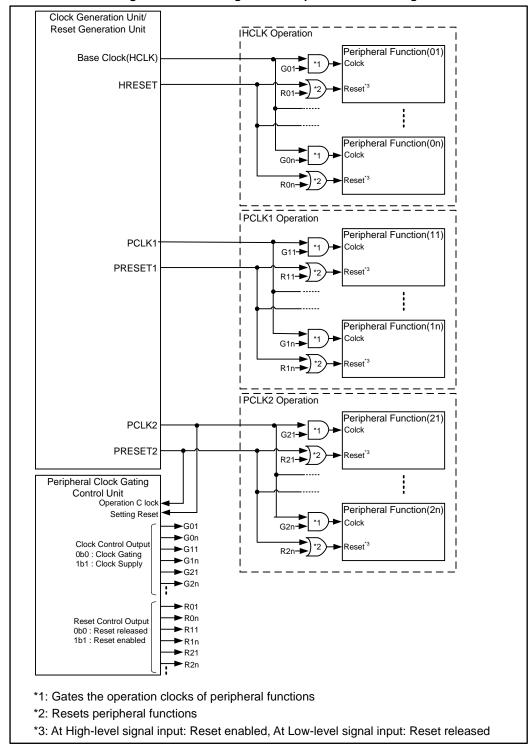

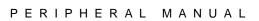

| CHAPTER 2-2: Peripheral Clock Gating                               | 81    |

| 1. Peripheral Clock Gating Overview                                | 82    |

| Peripheral Clock Gating Configuration                              | 85    |

| 3. Peripheral Clock Gating Control                                 | 87    |

| 3.1. Peripheral Clock Control Procedures                           | 88    |

| 4. Peripheral Clock Gating Function Registers                      | 91    |

| 4.1. Peripheral Function Clock Control Register 0 (CKEN0)          | 92    |

| 4.2. Peripheral Reset Control Register 0 (MRST0)                   | 95    |

| 4.3. Peripheral Clock Control Register 1 (CKEN1)                   | 98    |

| 4.4. Peripheral Function Reset Control Register 1 (MRST1)          | . 100 |

| 4.5. Peripheral Clock Control Register 2 (CKEN2)                   | . 102 |

| 4.6. Peripheral Function Reset Control Reset 2 (MRST2)             | . 107 |

| 5. Peripheral Clock Gating Function Usage Precautions              | . 111 |

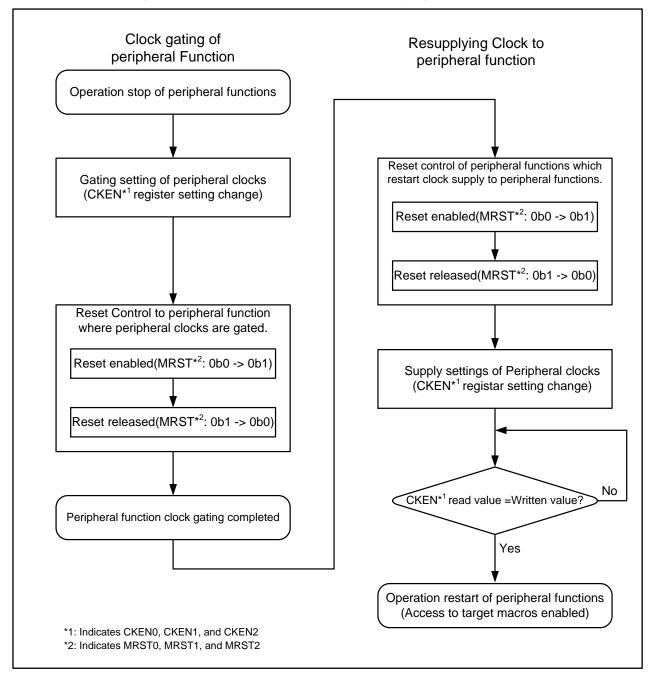

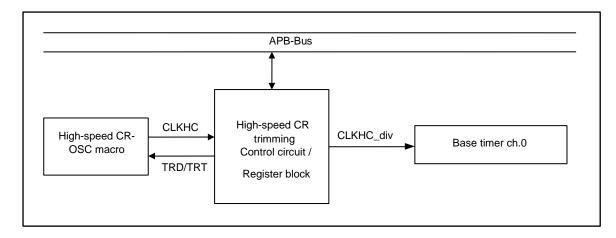

| CHAPTER 2-3: High-Speed CR Trimming                                | . 115 |

| 1. High-Speed CR Trimming Function Overview                        | . 116 |

| 2. High-Speed CR Trimming Function Configuration and Block Diagram | . 117 |

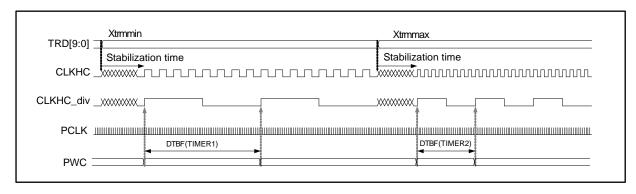

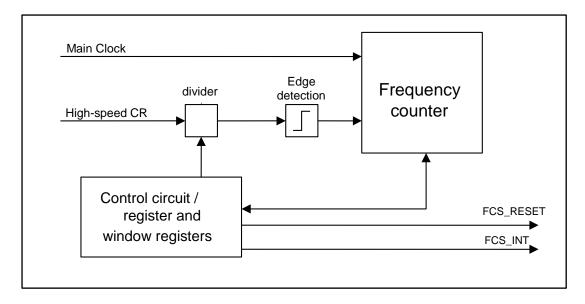

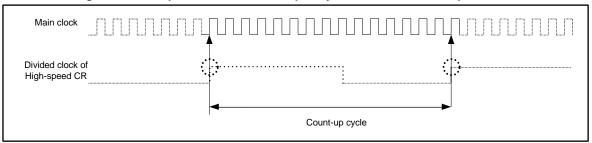

| 3. High-Speed CR Trimming Function Operation                       | . 118 |

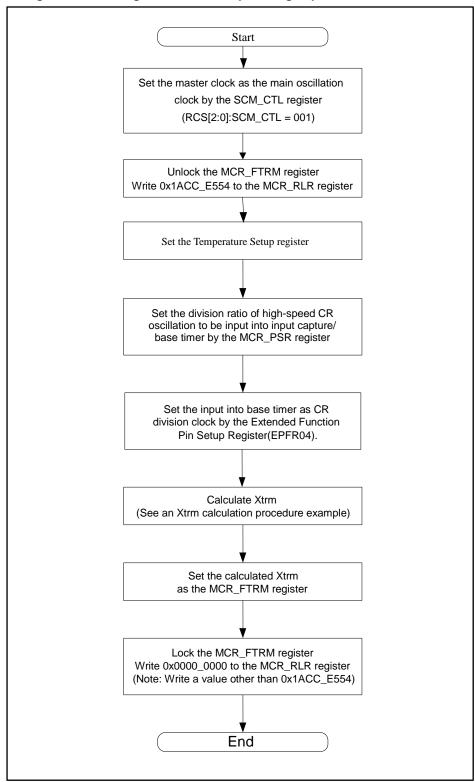

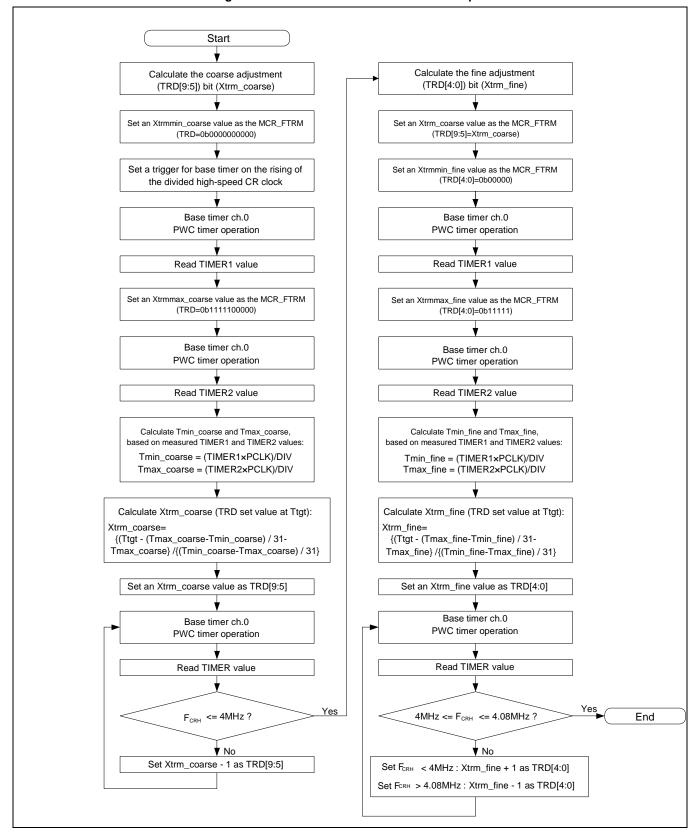

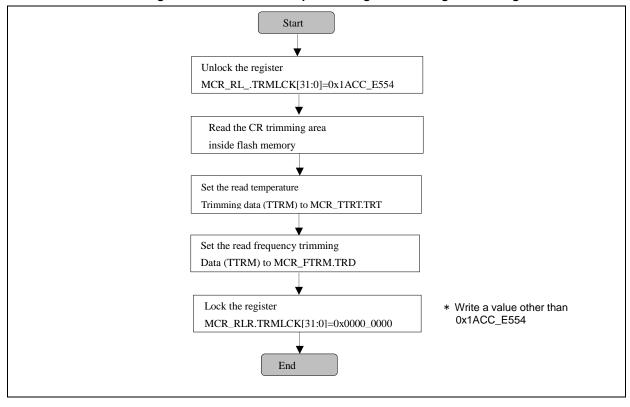

| 4. High-Speed CR Trimming Function Setup Procedure Example         | . 119 |

| 5. High-Speed CR Trimming Function Register List                                   |     |

|------------------------------------------------------------------------------------|-----|

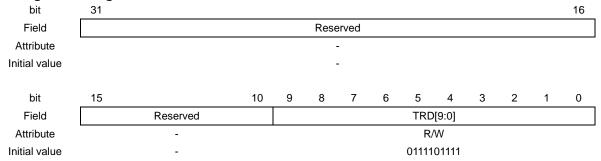

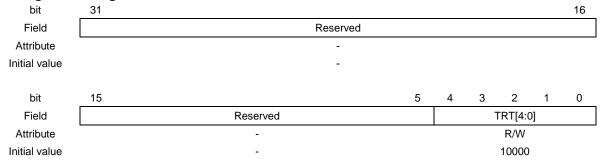

| 5.1. High-speed CR oscillation Frequency Division Setup Register (MCR_PSR)         | 127 |

| 5.2. High-speed CR oscillation Frequency Trimming Register (MCR_FTRM)              | 128 |

| 5.3. High-speed CR Oscillation Temperature Trimming Setup Register (MCR_TTRM)      | 129 |

| 5.4. High-Speed CR Oscillation Register Write-Protect Register (MCR_RLR)           |     |

| High-Speed CR Trimming Function Usage Precautions                                  | 131 |

| CHAPTER 2-4: Low-speed CR Prescaler                                                |     |

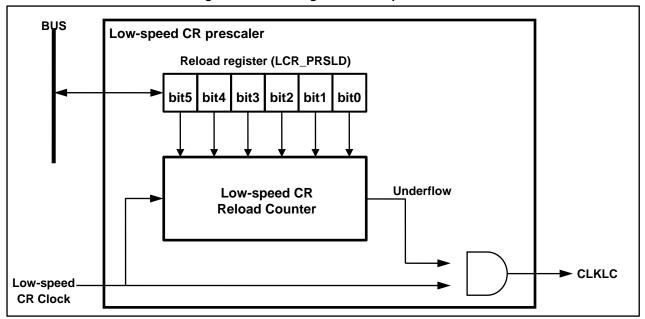

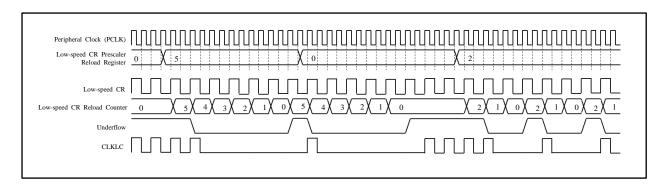

| 1. Low-speed CR Prescaler Overview                                                 | 134 |

| 2. Low-speed CR Prescaler Configuration                                            | 135 |

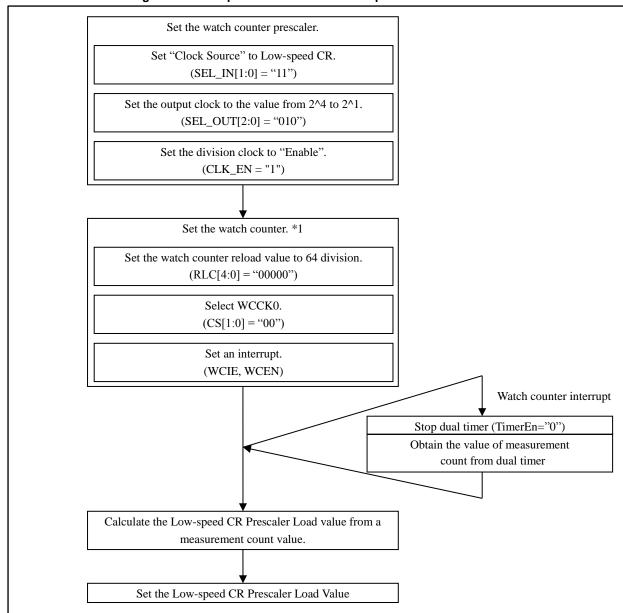

| 3. Low-speed CR Prescaler Operation and Setup Procedure Example                    | 136 |

| 4. Low-speed CR Prescaler Register                                                 | 139 |

| 4.1. Low-speed CR Prescaler Control Register (LCR_PRSLD)                           | 140 |

| CHAPTER 3: Clock supervisor                                                        | 141 |

| 1. Overview                                                                        | 142 |

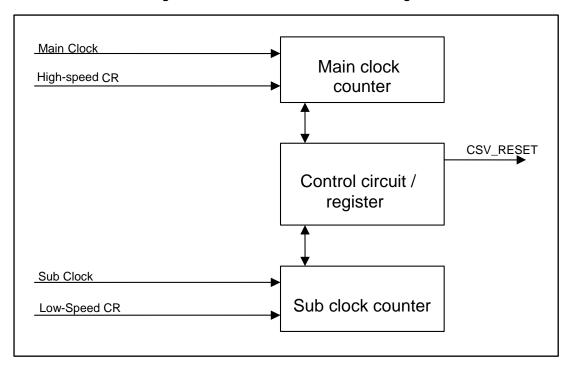

| 2. Configurations and Block Diagrams                                               | 143 |

| 3. Explanation of Operations                                                       | 145 |

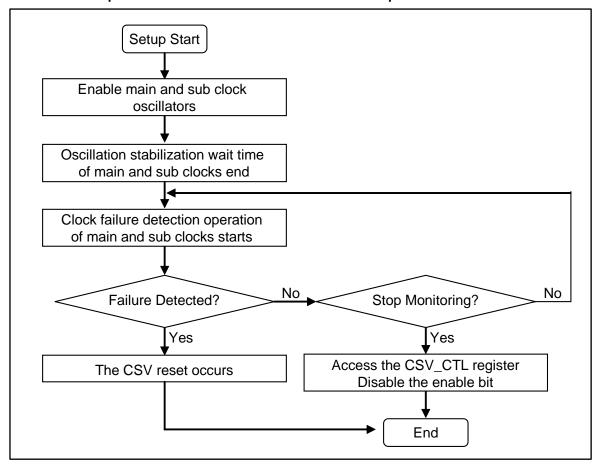

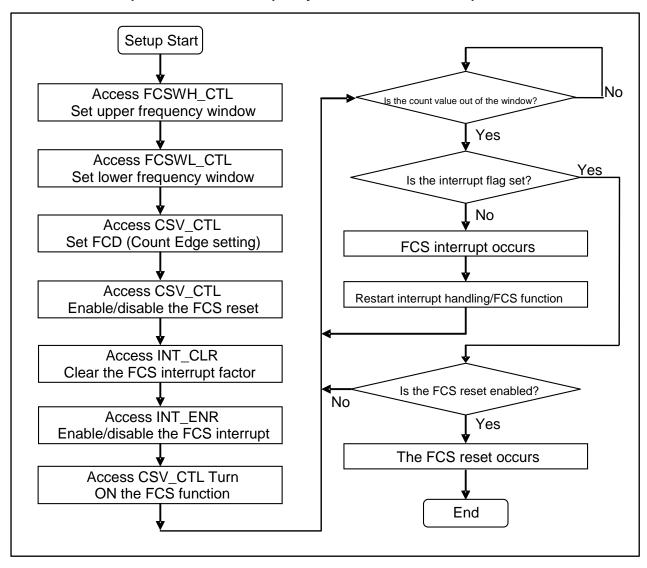

| 4. Setup Procedure Examples                                                        | 146 |

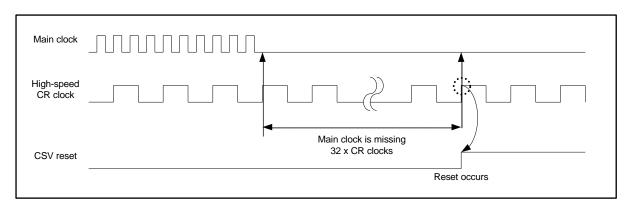

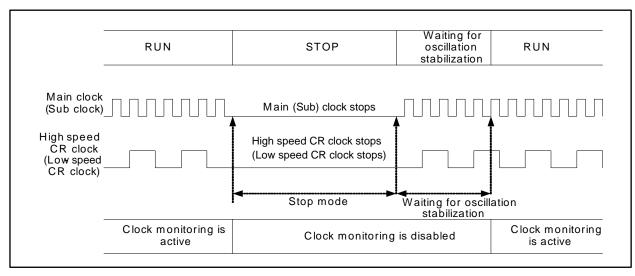

| 5. Operation Examples                                                              | 148 |

| 6. Registers                                                                       | 152 |

| 6.1. CSV control register (CSV_CTL)                                                | 153 |

| 6.2. CSV status register (CSV_STR)                                                 |     |

| 6.3. Frequency detection window setting register (Upper) (FCSWH_CTL)               |     |

| 6.4. Frequency detection window setting register (Lower) (FCSWL_CTL)               |     |

| 6.5. Frequency detection counter register (FCSWD_CTL)                              | 158 |

| 7. Usage Precautions                                                               |     |

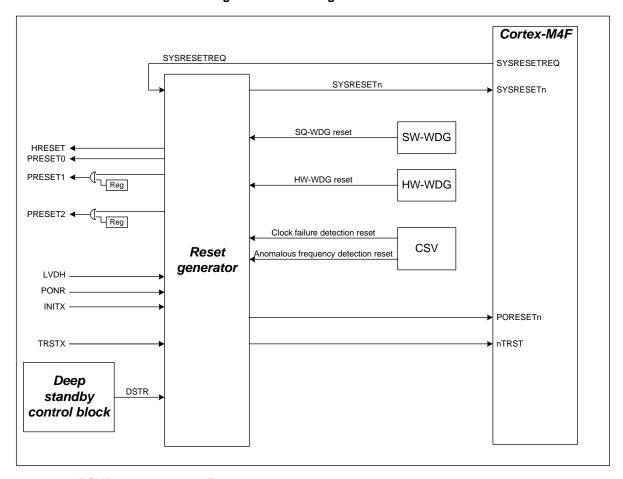

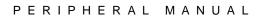

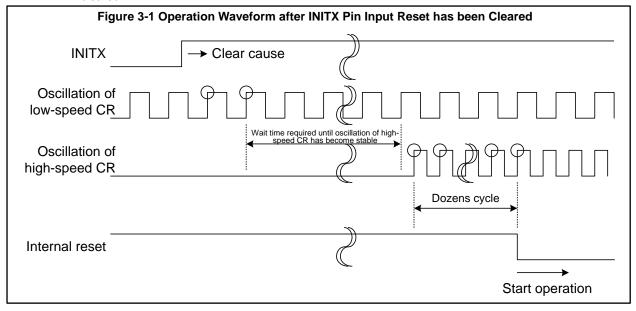

| CHAPTER 4: Resets                                                                  | 161 |

| 1. Overview                                                                        | 162 |

| 2. Configuration                                                                   | 163 |

| 3. Explanation of Operations                                                       | 164 |

| 3.1. Reset Factors                                                                 | 165 |

| 3.2. Resetting Inside the Device                                                   |     |

| 3.2.1. Resets to Cortex-M4                                                         |     |

| 3.2.2. Resets to Peripheral Circuit                                                |     |

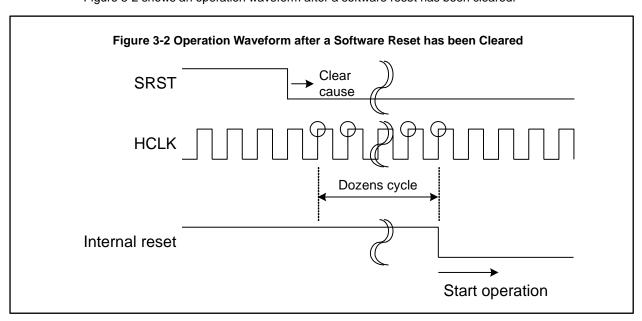

| 3.3. Reset Sequence                                                                |     |

| 3.4. Operations After Resets are Cleared                                           |     |

| 4. Register                                                                        | 174 |

| 4.1. Reset Factor Register (RST_STR: ReSeT STatus Register)                        |     |

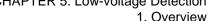

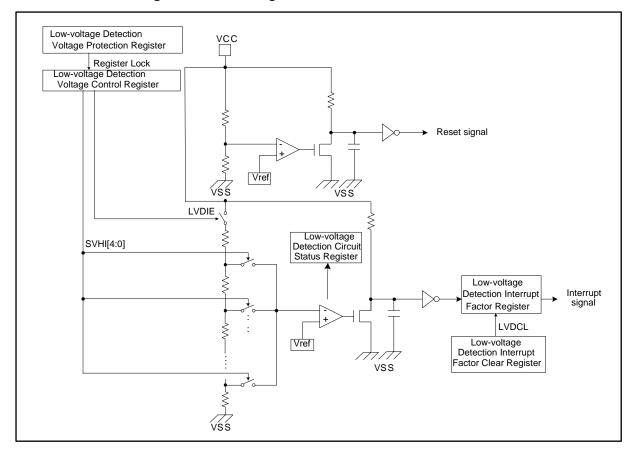

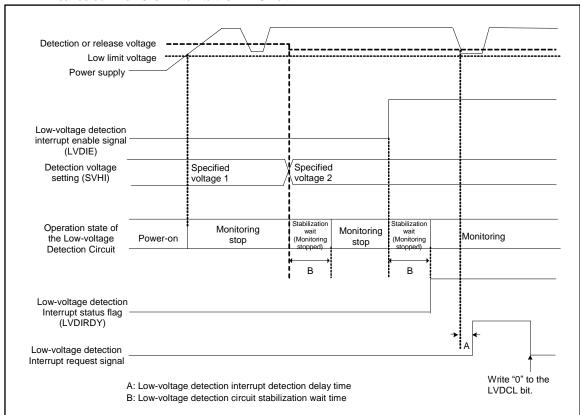

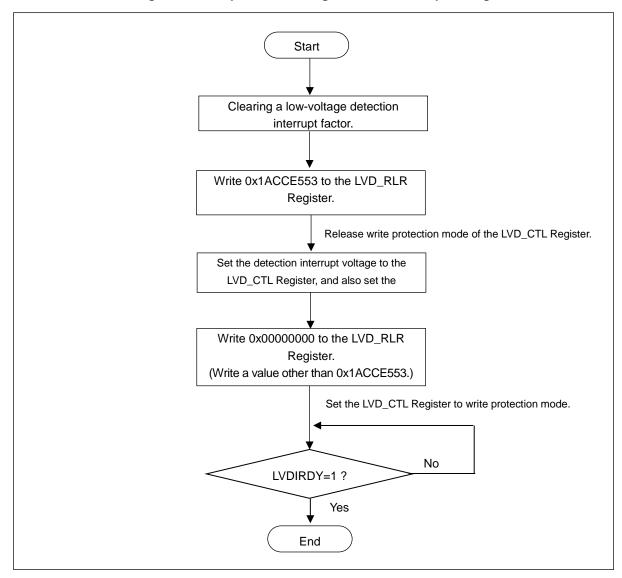

| CHAPTER 5: Low-voltage Detection                                                   |     |

| 1. Overview                                                                        | 178 |

| 2. Configuration                                                                   |     |

| 3. Explanation of Operations                                                       | 180 |

| 4. Setup Procedure Examples                                                        |     |

| 5. Registers                                                                       |     |

| 5.1. Low-voltage Detection Voltage Control Register (LVD_CTL)                      | 185 |

| 5.2. Low-voltage Detection Interrupt Factor Register (LVD_STR)                     |     |

| 5.3. Low-voltage Detection Interrupt Factor Clear Register (LVD_CLR)               |     |

| 5.4. Low-voltage Detection Voltage Protection Register (LVD_RLR)                   |     |

| 5.5. Low-voltage Detection Circuit Status Register (LVD_STR2)                      |     |

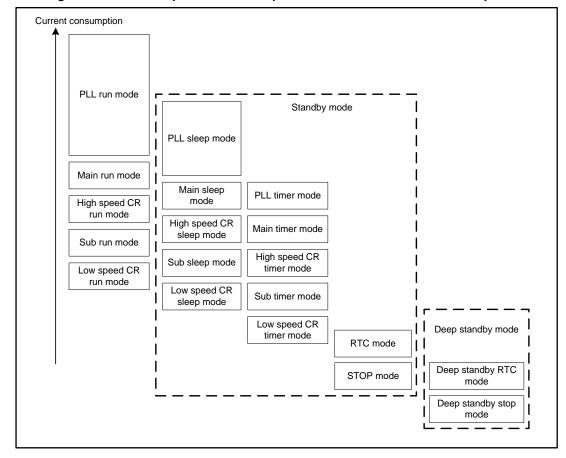

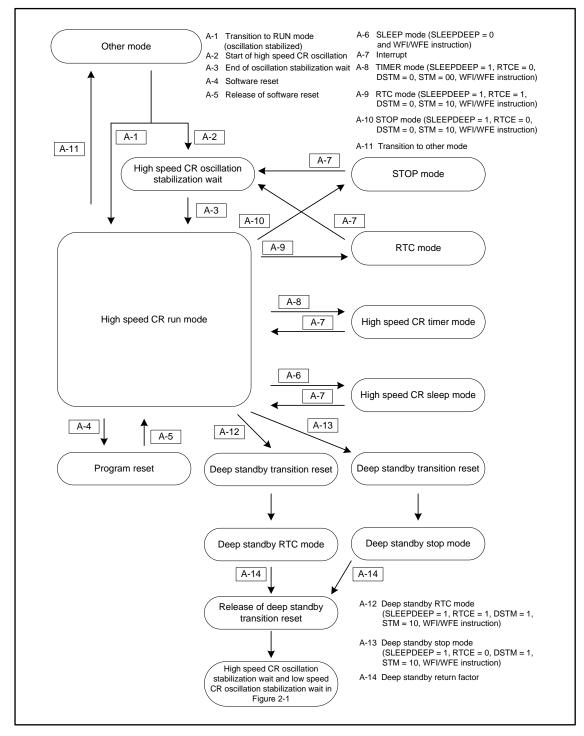

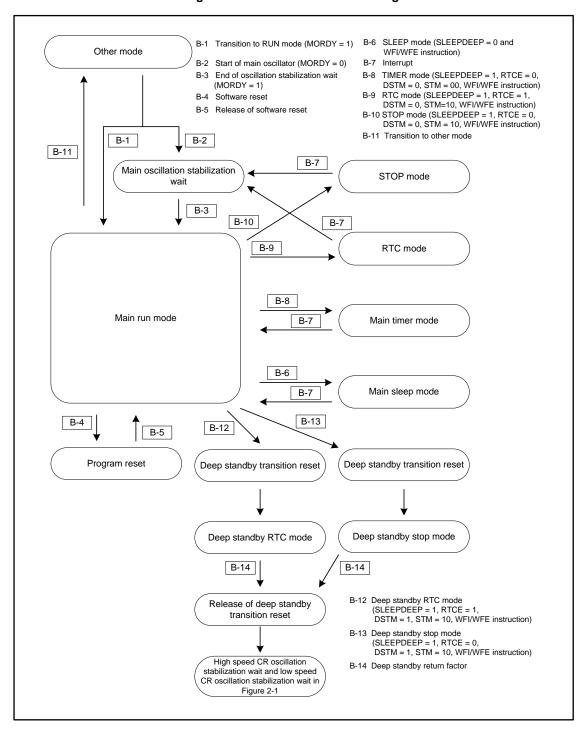

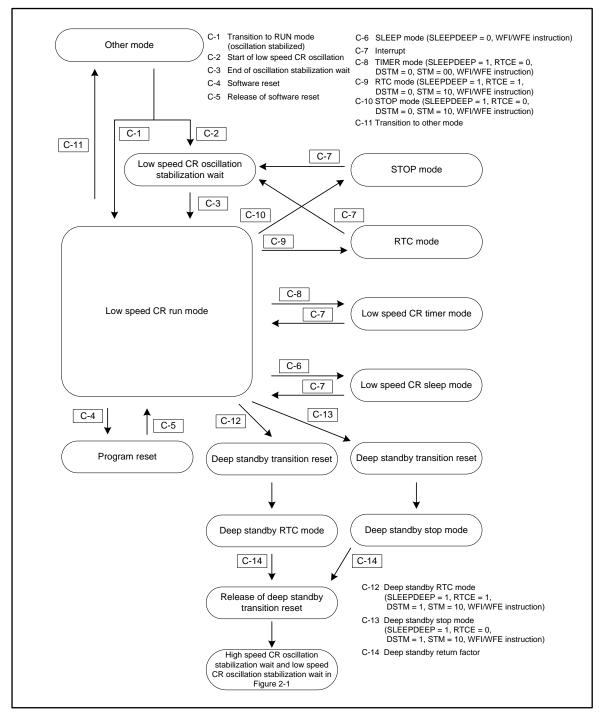

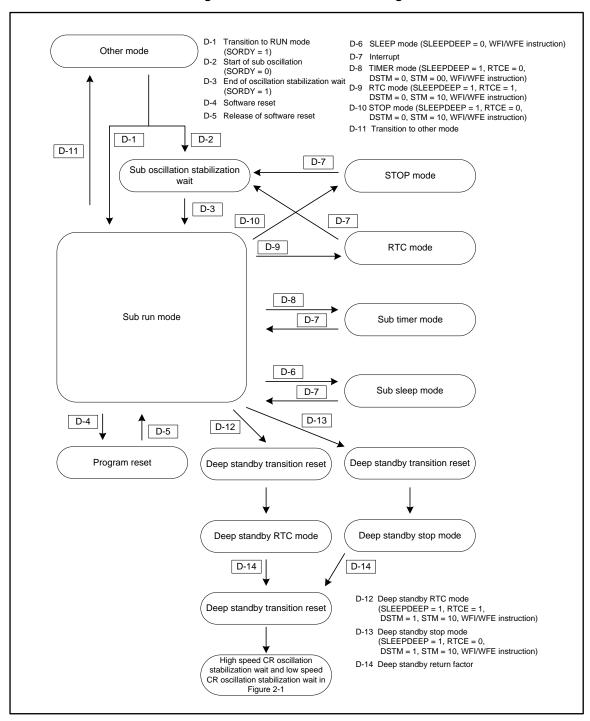

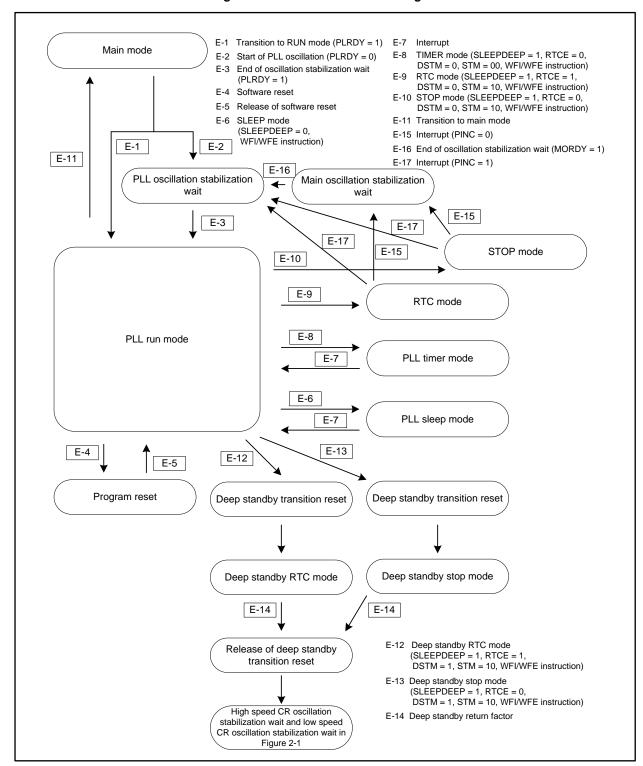

| CHAPTER 6: Low Power Consumption Mode                                              |     |

| Overview of Low Power Consumption Mode                                             |     |

| 2. Configuration of CPU Operation Modes                                            |     |

| 3. Operations in Standby Modes                                                     |     |

| 3.1. Operations in Sleep Modes (High Speed CR Sleep Mode, Main Sleep Mode, PLL Sle |     |

| Low Speed CR Sleep Mode, Sub Sleep Mode)                                           | -   |

| 3.2. Operations in Timer Modes (High Speed CR Timer Mode, Main Timer Mode, PLL Tin |     |

| Low Speed CR Timer Mode, Sub Timer Mode)                                           |     |

| 3.3. Operations in RTC Mode                                                        | 211 |

| 3.4. Operations in Stop Mode                                             | 214 |

|--------------------------------------------------------------------------|-----|

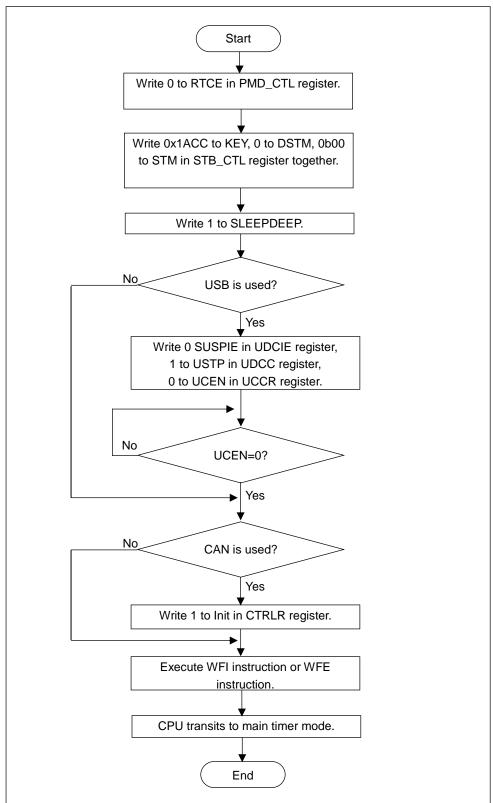

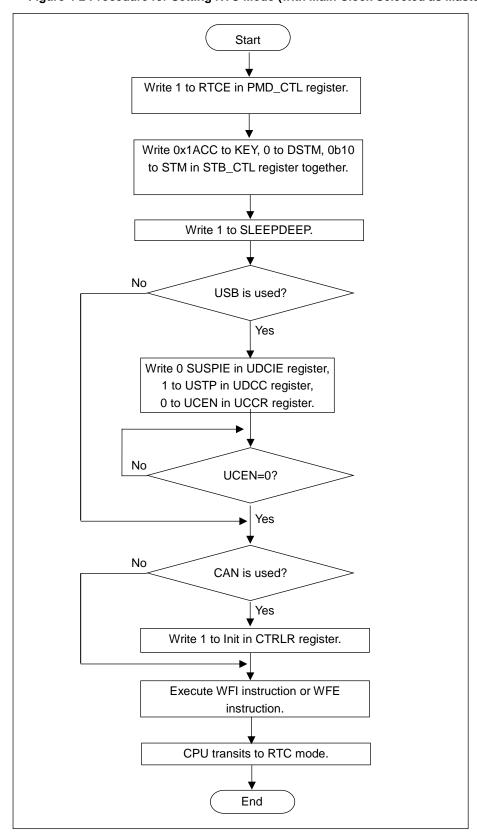

| 4. Examples of Procedure for Setting Standby Mode                        | 217 |

| 5. Operations in Deep Standby Modes                                      | 221 |

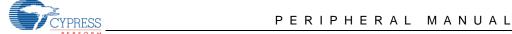

| 5.1. Operations in Deep Standby RTC Mode                                 | 223 |

| 5.2. Operations in Deep Standby Stop Mode                                | 225 |

| 6. Examples of Procedure for Setting Deep Standby Mode                   | 227 |

| 7. Procedure for Determining Factor for Returning from Deep Standby Mode | 229 |

| 8. List of Low Power Consumption Mode Registers                          | 230 |

| 8.1. Standby Mode Control Register (STB_CTL)                             | 231 |

| 8.2. Sub Clock Supply Control Register (RCK_CTL)                         | 233 |

| 8.3. RTC Mode Control Register (PMD_CTL)                                 | 234 |

| 8.4. Deep Standby Return Factor Register 1 (WRFSR)                       | 235 |

| 8.5. Deep Standby Return Factor Register 2 (WIFSR)                       | 236 |

| 8.6. Deep Standby Return Enable Register (WIER)                          |     |

| 8.7. WKUP Pin Input Level Register (WILVR)                               |     |

| 8.8. Deep Standby RAM Retention Register (DSRAMR)                        | 241 |

| 8.9. Backup Registers 01 to 16 (BUR01 to BUR16)                          | 242 |

| 9. Usage Precautions                                                     |     |

| CHAPTER 7-1: VBAT Domain Configuration                                   | 245 |

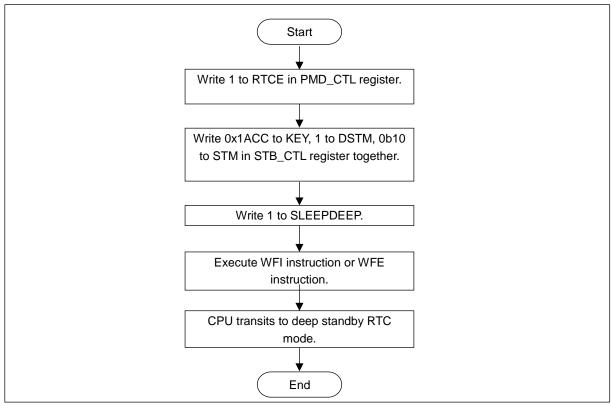

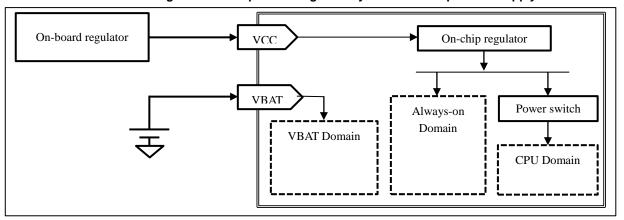

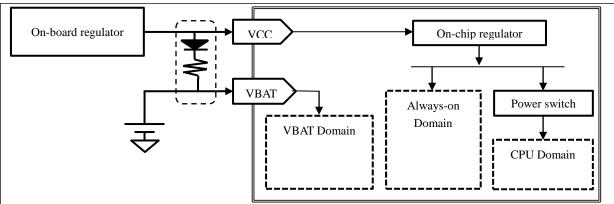

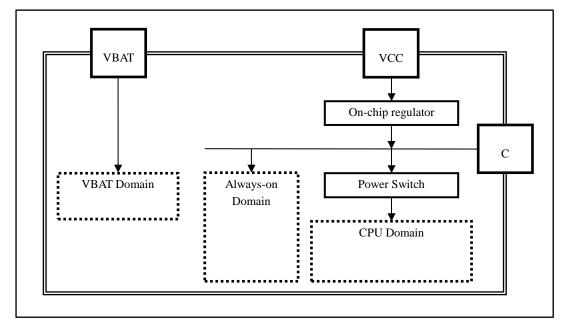

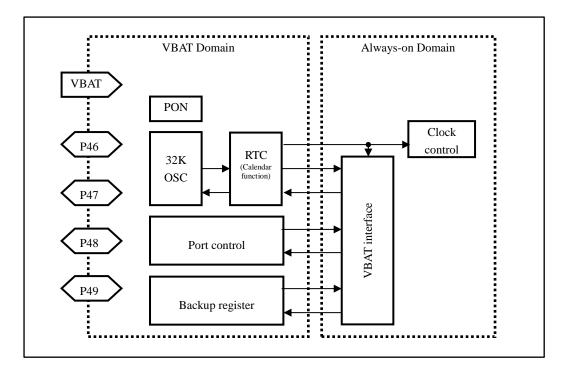

| 1. Configuration                                                         | 246 |

| CHAPTER 7-2: VBAT Domain(A)                                              | 247 |

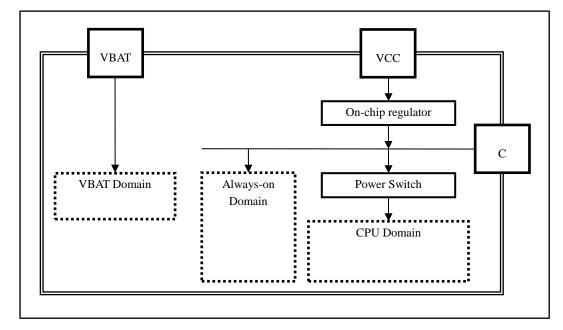

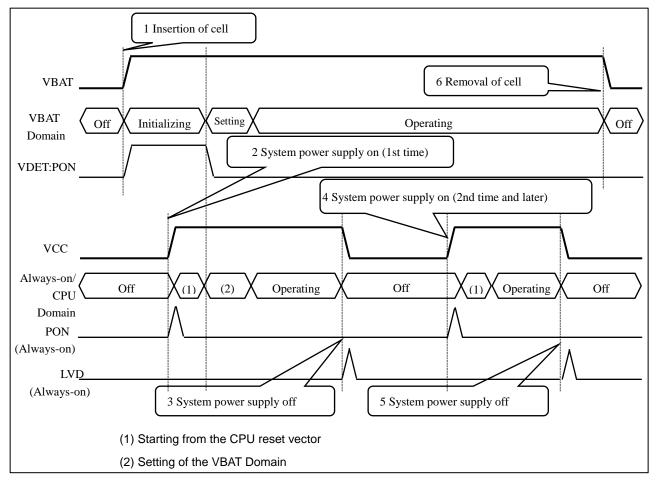

| 1. Overview of VBAT Domain                                               | 248 |

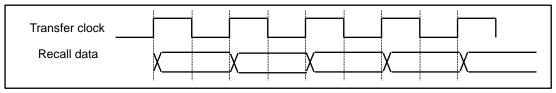

| 2. Configuration of VBAT Domain                                          | 250 |

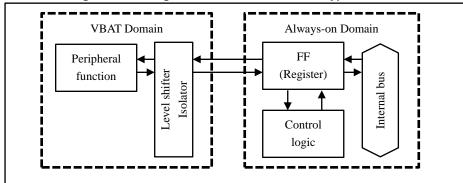

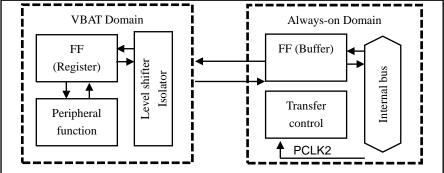

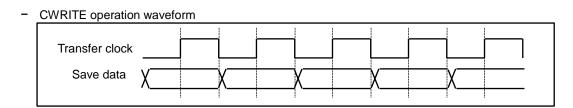

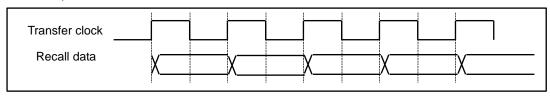

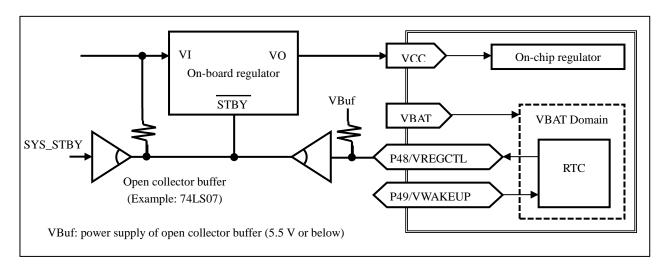

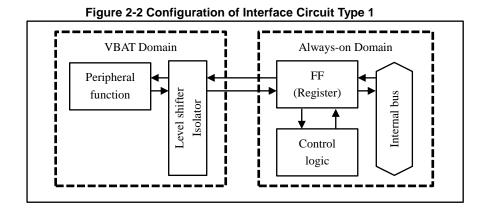

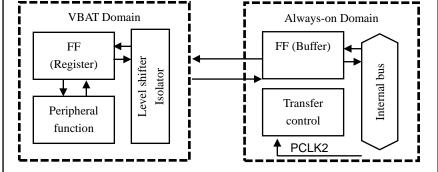

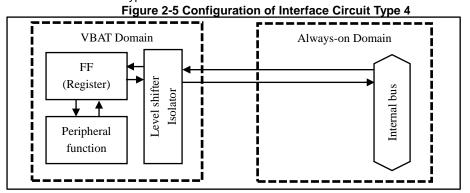

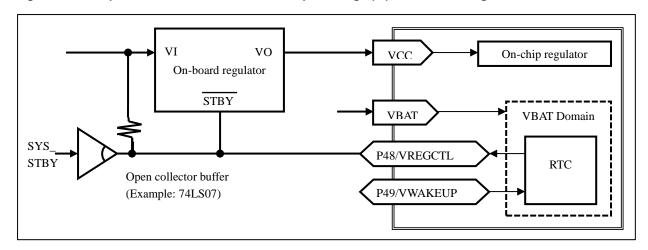

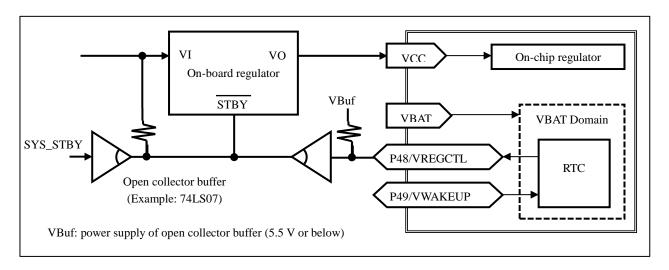

| 2.1. Interfacing with Always-on Domain                                   | 251 |

| 2.2. RTC                                                                 | 261 |

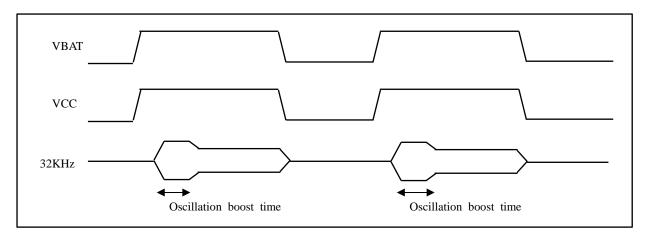

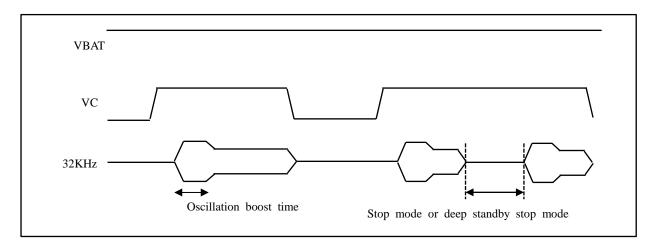

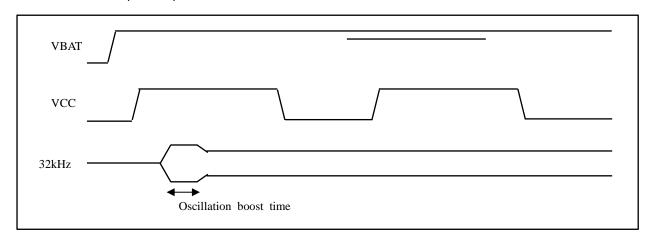

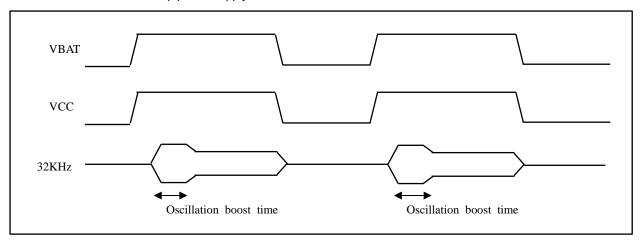

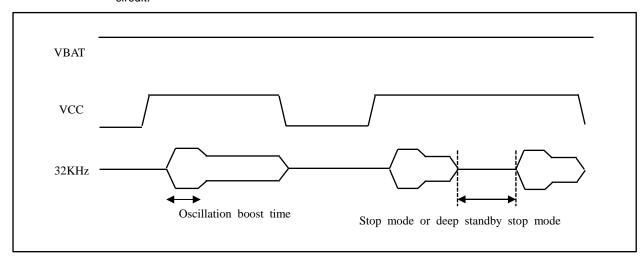

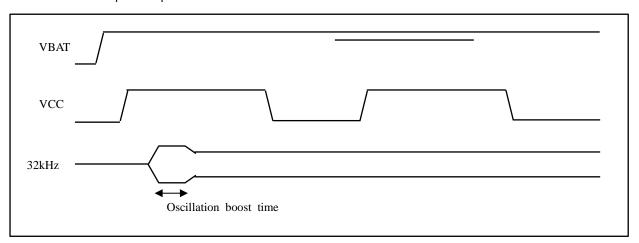

| 2.3. 32 kHz Oscillation Circuit                                          | 262 |

| 2.4. Power-on circuit                                                    | 264 |

| 2.5. Backup Registers                                                    | 265 |

| 2.6. VBAT I/O Ports                                                      | 267 |

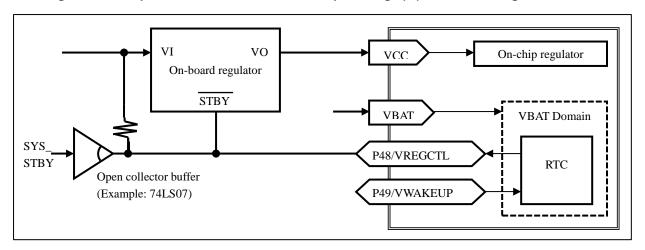

| 3. Chip Power Supply Control                                             | 270 |

| 4. Hibernation Control                                                   | 273 |

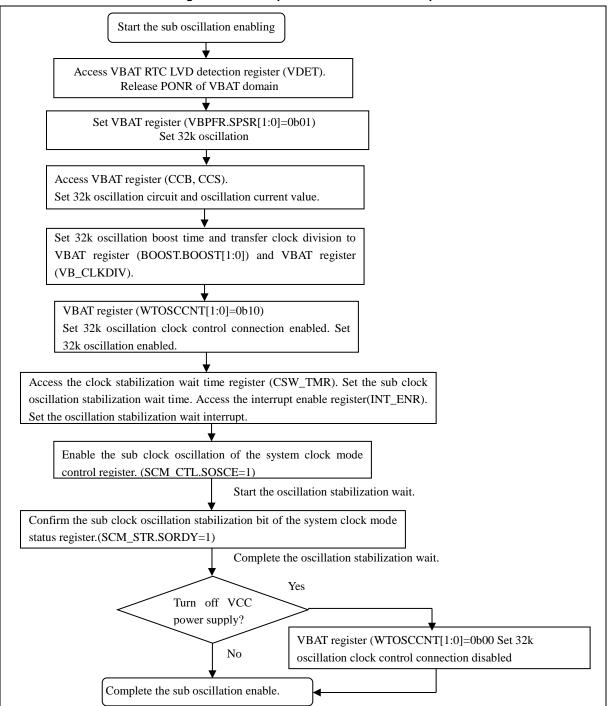

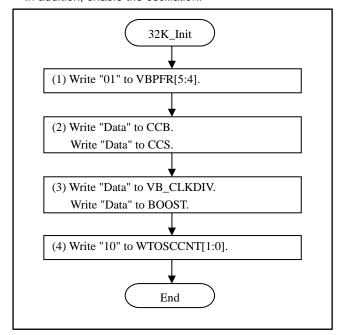

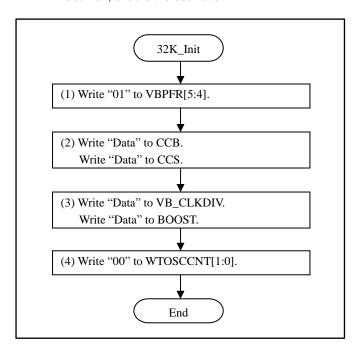

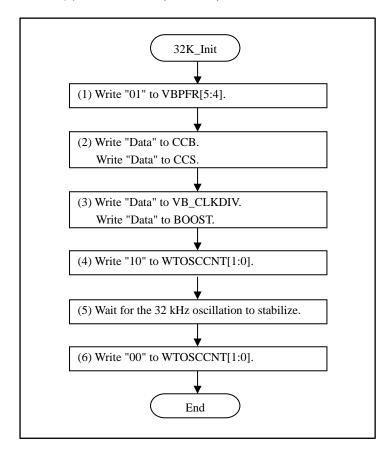

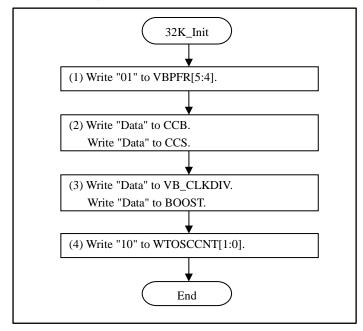

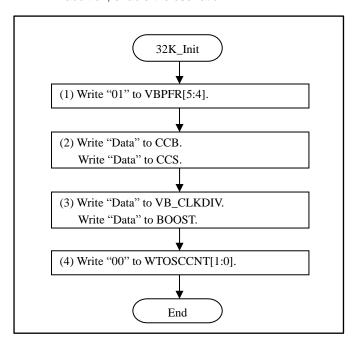

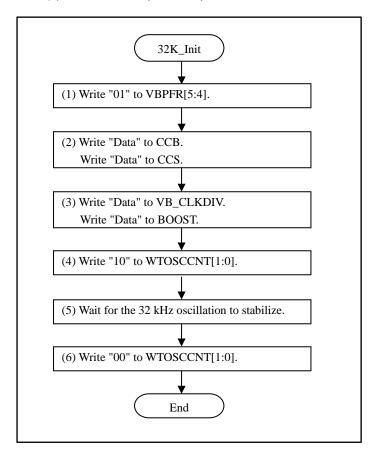

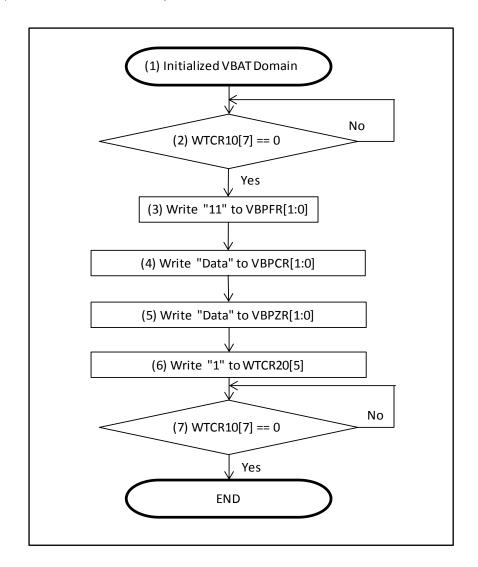

| 5. Procedure for Setting 32 kHz Clock                                    | 277 |

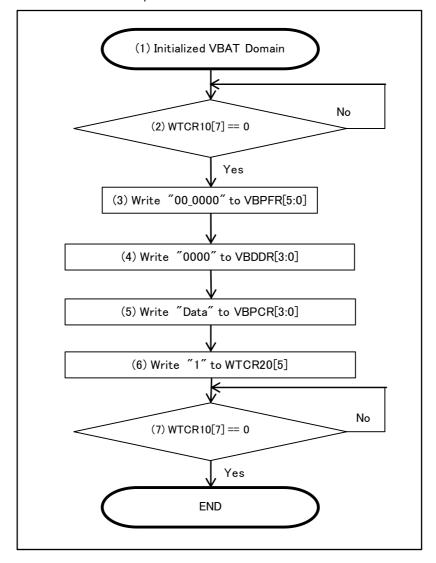

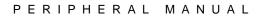

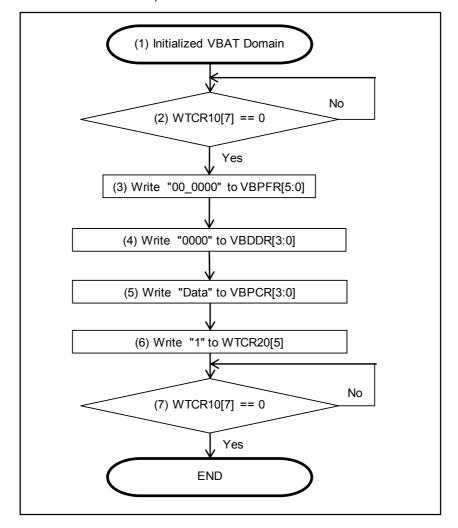

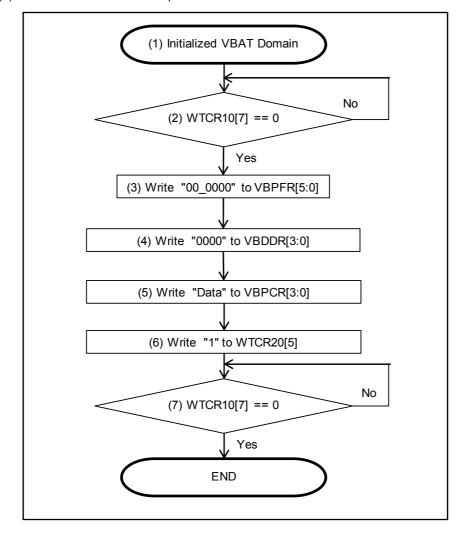

| 6. Procedure for Setting VBAT I/O Port                                   | 281 |

| 7. Registers                                                             | 284 |

| 7.1. VB_CLKDIV Register                                                  | 285 |

| 7.2. WTOSCCNT Register                                                   | 286 |

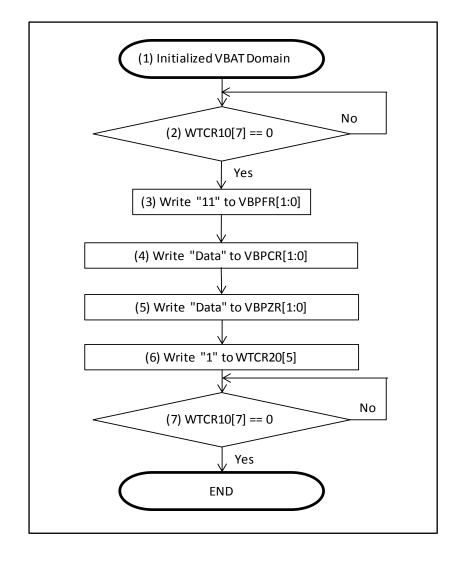

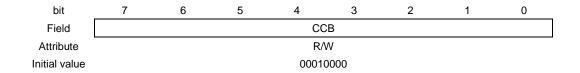

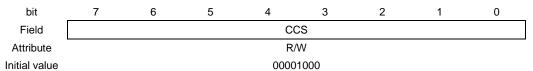

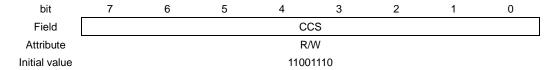

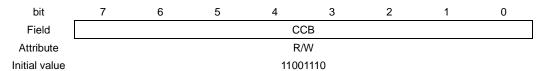

| 7.3. CCS/CCB Register                                                    | 287 |

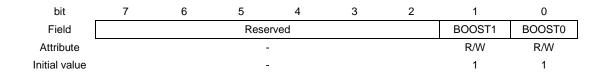

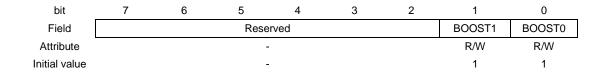

| 7.4. BOOST Register                                                      | 288 |

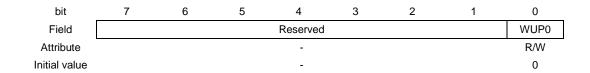

| 7.5. EWKUP Register                                                      | 289 |

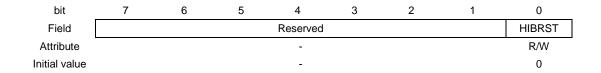

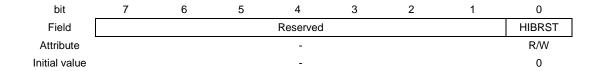

| 7.6. HIBRST Register                                                     | 290 |

| 7.7. VDET Register                                                       |     |

| 7.8. Port Function Set Register (VBPFR)                                  | 292 |

| 7.9. Pull-up Set Register (VBPCR)                                        |     |

| 7.10. Port I/O Direction Set Register (VBDDR)                            | 295 |

| 7.11. Port Input Data Register (VBDIR)                                   |     |

| 7.12. Port Output Data Register (VBDOR)                                  | 297 |

| 7.13. Port Pseudo-Open Drain Set Register (VBPZR)                        | 298 |

| 8. Usage Precautions                                                     |     |

| CHAPTER 7-3: VBAT Domain(B)                                              |     |

| 1. Overview of VBAT Domain                                               |     |

| 2. Configuration of VBAT Domain                                          |     |

| 2.1. Interfacing with Always-on Domain                                   |     |

| 2.2. RTC                                                                 |     |

| 2.3. 32 kHz Oscillation Circuit                                          |     |

| 2.4. Power-on circuit                                                    |     |

| 2.5. Backup Registers                                                    |     |

| 2.6. VBAT I/O Ports                                                      | 321 |

| 3. Chip Power Supply Control                                                         | . 324 |

|--------------------------------------------------------------------------------------|-------|

| 4. Hibernation Control                                                               | . 327 |

| 5. Procedure for Setting 32 kHz Clock                                                | . 331 |

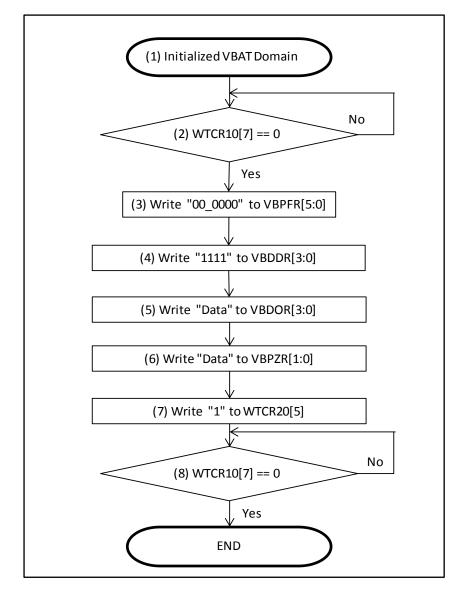

| 6. Procedure for Setting VBAT I/O Port                                               | . 335 |

| 7. Registers                                                                         | . 338 |

| 7.1. VB_CLKDIV Register                                                              | . 339 |

| 7.2. WTOSCCNT Register                                                               | . 340 |

| 7.3. CCS/CCB Register                                                                | . 341 |

| 7.4. BOOST Register                                                                  | . 343 |

| 7.5. EWKUP Register                                                                  | . 344 |

| 7.6. HIBRST Register                                                                 | . 345 |

| 7.7. VDET Register                                                                   | . 346 |

| 7.8. Port Function Set Register (VBPFR)                                              | . 347 |

| 7.9. Pull-up Set Register (VBPCR)                                                    | . 349 |

| 7.10. Port I/O Direction Set Register (VBDDR)                                        | . 350 |

| 7.11. Port Input Data Register (VBDIR)                                               | . 351 |

| 7.12. Port Output Data Register (VBDOR)                                              | . 352 |

| 7.13. Port Pseudo-Open Drain Set Register (VBPZR)                                    | . 353 |

| 8. Usage Precautions                                                                 | . 354 |

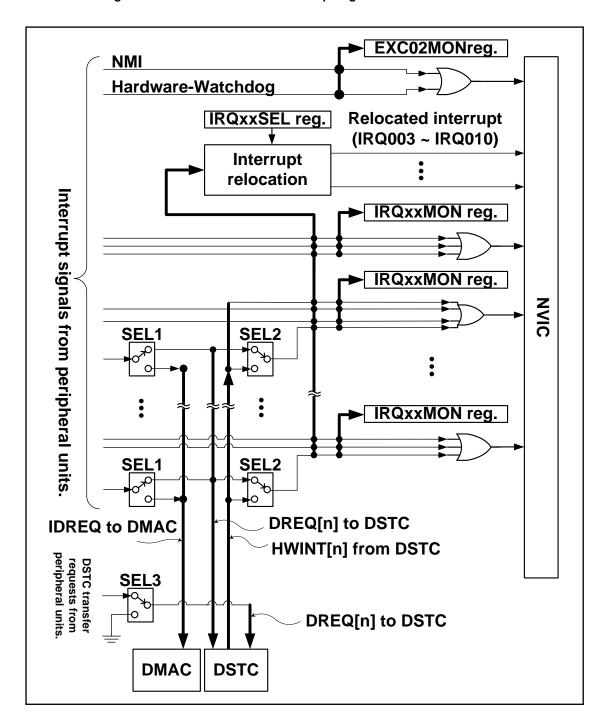

| CHAPTER 8: Interrupts                                                                | . 355 |

| 1. Overview                                                                          | . 356 |

| 2. Lists of Interrupts                                                               | . 360 |

| 3. Registers                                                                         | . 381 |

| 3.1. DMAC DMA Request Selection Register (DRQSEL)                                    | . 384 |

| 3.2. Relocate Interrupt Selection Register (IRQxxxSEL)                               | . 386 |

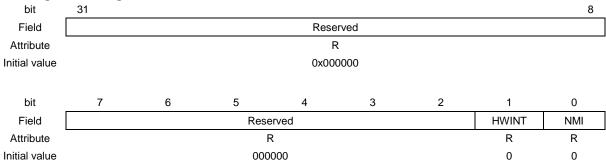

| 3.3. EXC02 Batch Read Register (EXC02MON)                                            | . 388 |

| 3.4. IRQ000 Batch Read Register (IRQ000MON)                                          | . 389 |

| 3.5. IRQ001 Batch Read Register (IRQ001MON)                                          | . 390 |

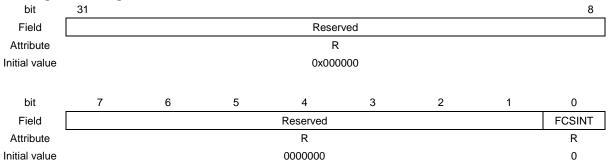

| 3.6. IRQ002 Batch Read Register (IRQ002MON)                                          | . 391 |

| 3.7. IRQ003/004/005/006/007/008/009/010 Batch Read Register (IRQxxxMON)              | . 392 |

| 3.8. IRQ011/012/013/014/015/016/017/018/051/052/053/054/055/056/057/058 Batch Read   |       |

| Register (IRQxxxMON)                                                                 |       |

| 3.9. IRQ019/020/096/097 Batch Read Register (IRQxxxMON)                              |       |

| 3.10. IRQ021/022/023 Batch Read Register (IRQxxxMON)                                 |       |

| 3.11. IRQ024/028/032 Batch Read Register (IRQxxxMON)                                 |       |

| 3.12. IRQ025/029/033 Batch Read Register (IRQxxxMON)                                 |       |

| 3.13. IRQ026/030/034 Batch Read Register (IRQxxxMON)                                 |       |

| 3.14. IRQ027/031/035 Batch Read Register (IRQxxxMON)                                 |       |

| 3.15. IRQ036/037/038 Batch Read Register (IRQxxxMON)                                 | . 401 |

| 3.16. IRQ039/040/041/042/043/044/045/046/098/099/100/101 Batch Read Register         |       |

| (IRQxxxMON)                                                                          |       |

| 3.17. IRQ047 Batch Read Register (IRQ047MON)                                         |       |

| 3.18. IRQ048 Batch Read Register (IRQ048MON)                                         |       |

| 3.19. IRQ049 Batch Read Register (IRQ049MON)                                         |       |

| 3.20. IRQ050 Batch Read Register (IRQ050MON)                                         |       |

| 3.21. IRQ059 Batch Read Register (IRQ059MON)                                         | . 408 |

| 3.22. IRQ060/062/064/066/068/070/072/074/103/105/107/109/120/122/124/126 Batch Read  |       |

| Register (IRQxxxMON)                                                                 |       |

| 3.23. IRQ061/063/065/067/069/071/073/075/104/106/108/110/ 121/123/125/127 Batch Read |       |

| Register (IRQxxxMON)                                                                 |       |

| 3.24. IRQ076/077/111 Batch Read Register (IRQxxxMON)                                 |       |

| 3.25. IRQ078/113 Batch Read Register (IRQxxxMON)                                     |       |

| 3.26. IRQ079/114 Batch Read Register (IRQxxxMON)                                     |       |

| 3.27. IRQ080 Batch Read Register (IRQ080MON)                                         |       |

| 3.28. IRQ081 Batch Read Register (IRQ081MON)                                         |       |

| 3.29. IRQ082 Batch Read Register (IRQ082MON)                                         |       |

| 3.30. IRQ083/084/085/086/087/088/089/090 Batch Read Register (IRQxxxMON)             | . 421 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 422               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3.32. IRQ092/093/094/095 Batch Read Register (IRQxxxMON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 423               |

| 3.33. IRQ102 Batch Read Register (IRQ102MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 425               |

| 3.34. IRQ112 Batch Read Register (IRQ112MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 426               |

| 3.35. IRQ115 Batch Read Register (IRQ115MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 428               |

| 3.36. IRQ117 Batch Read Register (IRQ117MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 429               |

| 3.37. IRQ118 Batch Read Register (IRQ118MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 430               |

| 3.38. IRQ119 Batch Read Register (IRQ119MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 431               |

| 3.39. IRQ116 Batch Read Register (IRQ116MON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 432               |

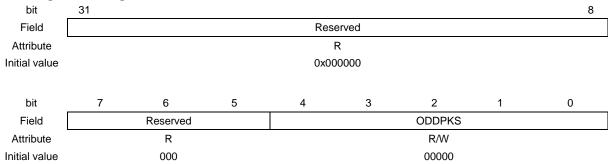

| 3.40. USB ch.0 Odd Packet Size DMA Enable Register (ODDPKS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 433               |

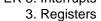

| 3.41. USB ch.1 Odd Packet Size DMA Enable Register (ODDPKS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 435               |

| 4. Usage Precautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 437               |

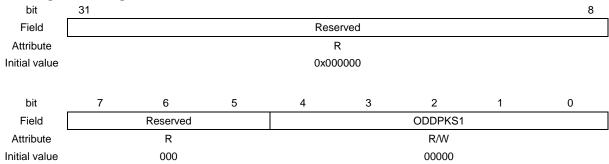

| CHAPTER 9: External Interrupt and NMI Control Sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 439               |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 440               |

| 2. Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 440               |

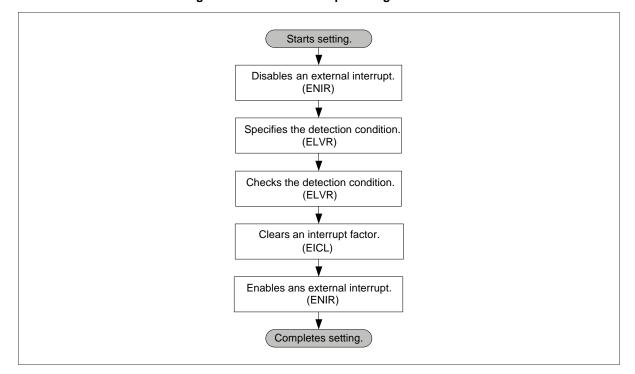

| Operations and Setting Procedure Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

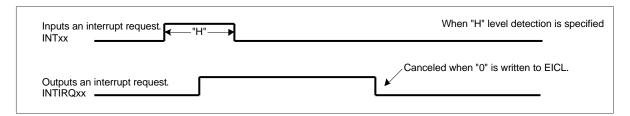

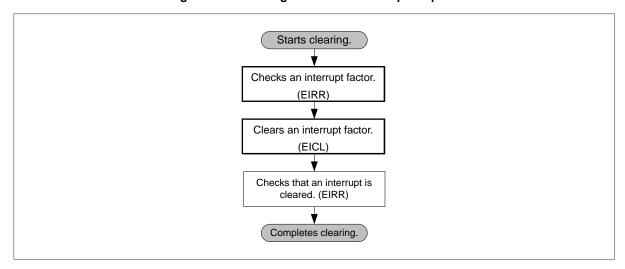

| 3.1. Operations of external interrupt control section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 3.2. Operations of NMI control section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 444               |

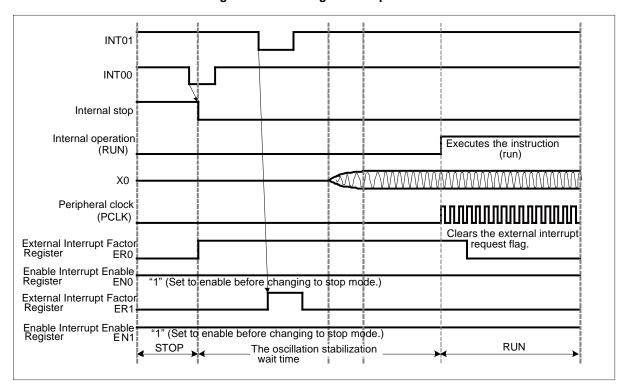

| 3.3. Returning from timer or stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 445               |

| 4. Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 446               |

| 4.1. External Interrupt Enable Register (ENIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| 4.2. External Interrupt Factor Register (EIRR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 448               |

| 4.3. External Interrupt Factor Clear Register (EICL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 449               |

| 4.4. External Interrupt Factor Level Register (ELVR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 450               |

| 4.5. External Interrupt Factor Level Register 1 (ELVR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 451               |

| 4.6. Non Maskable Interrupt Factor Register (NMIRR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 452               |

| 4.7. Non Maskable Interrupt Factor Clear Register (NMICL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 453               |

| 4.8. External Interrupt Factor Level Register 2 (ELVR2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| CHAPTER 10: DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| 1. Overview of DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 456               |

| 2. Configuration of DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 457               |

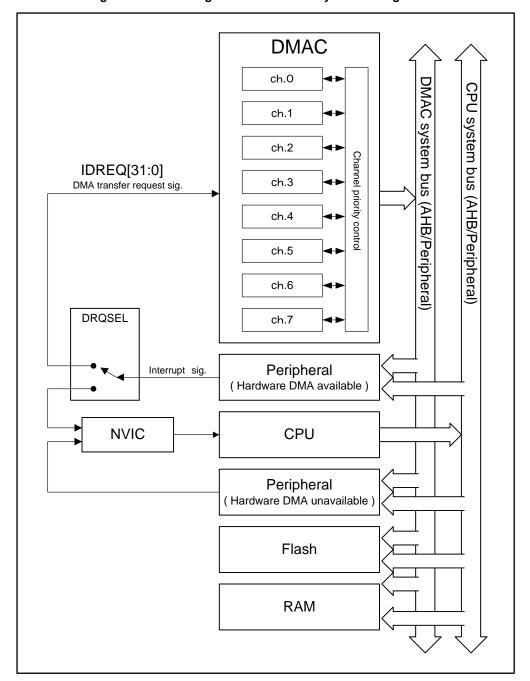

| 2.1. DMAC and System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| 2.2. I/O Signals of DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 3. Functions and Operations of DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 400               |

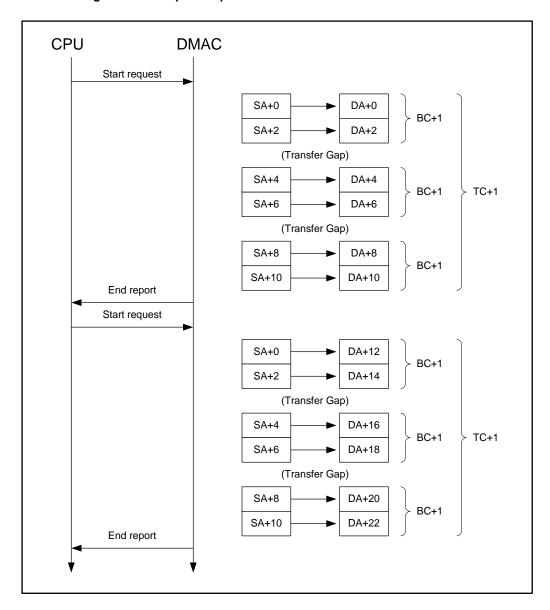

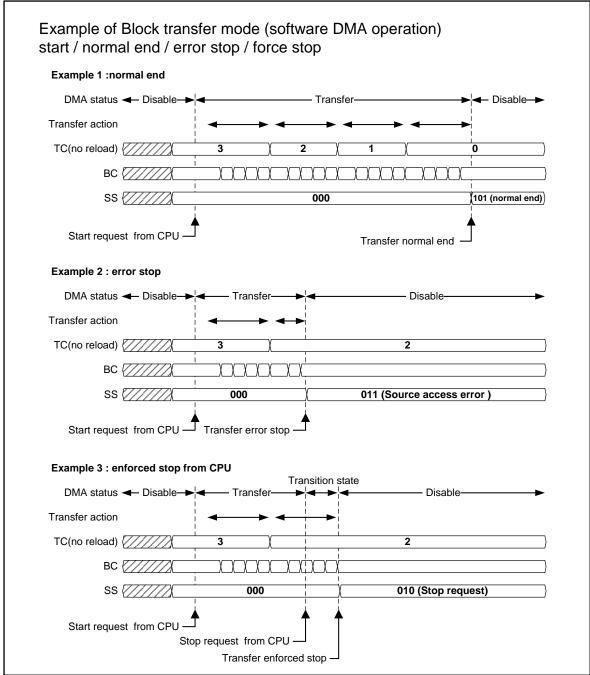

| 3.1. Software-Block Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 463               |

| 3.1. Software-Block Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

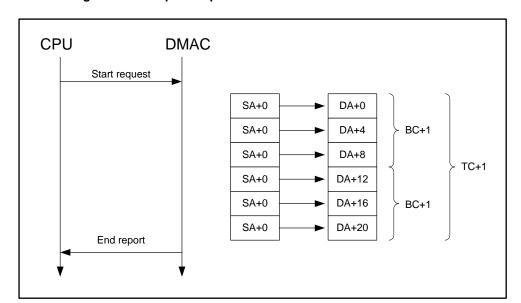

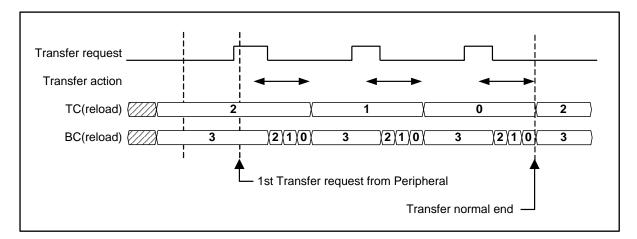

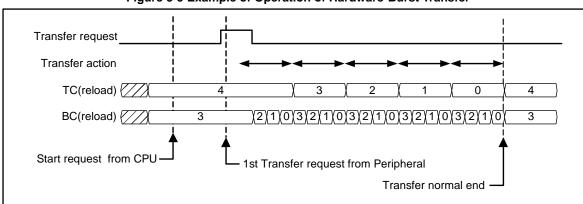

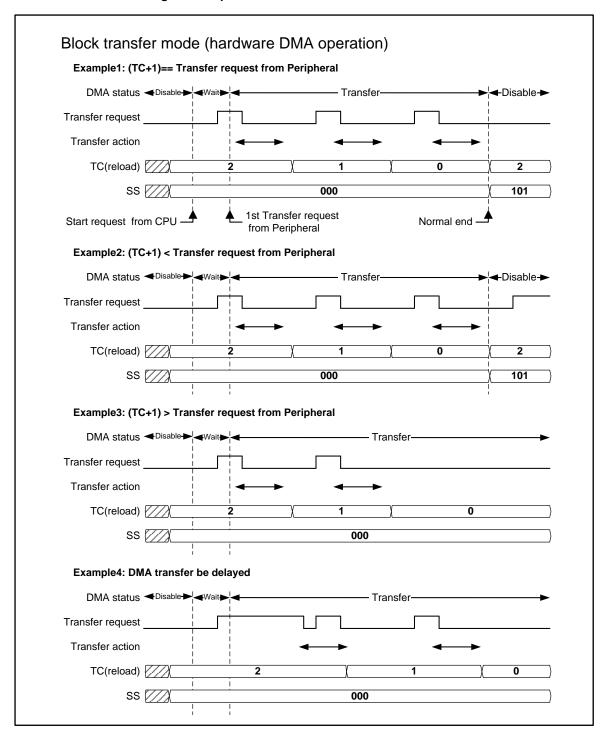

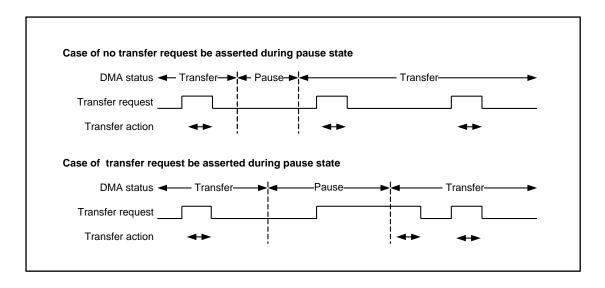

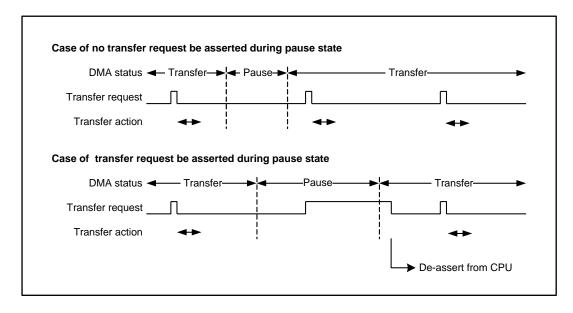

| 3.2. Software-Burst Transfer      3.3. Hardware-Demand Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 465<br>466        |

| 3.2. Software-Burst Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 465<br>466        |

| 3.2. Software-Burst Transfer      3.3. Hardware-Demand Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 465<br>466<br>467 |

| 3.2. Software-Burst Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

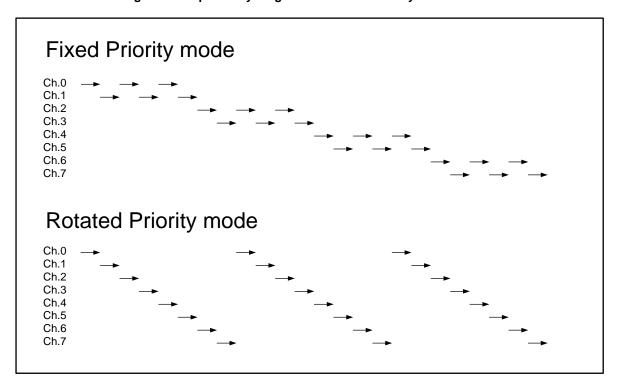

| 3.2. Software-Burst Transfer  3.3. Hardware-Demand Transfer  3.4. Hardware-Block Transfer & Burst Transfer  3.5. Channel Priority Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| 3.2. Software-Burst Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

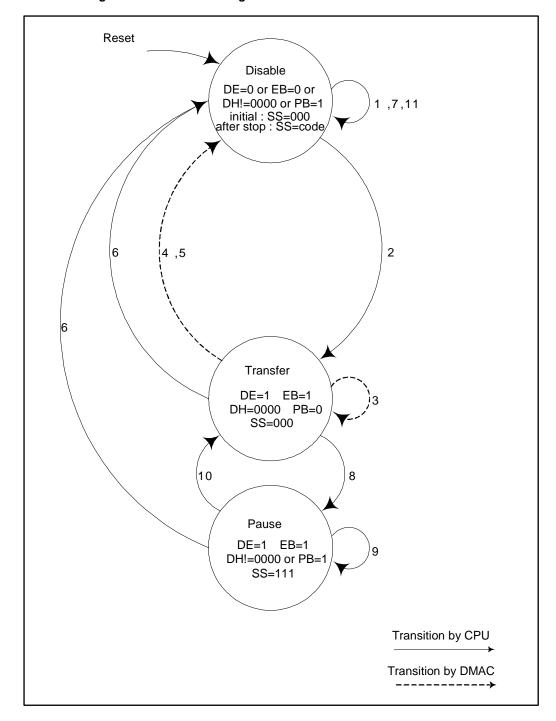

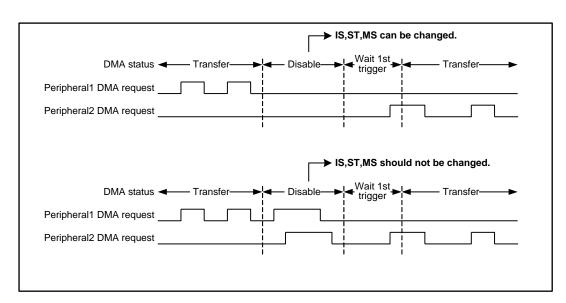

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control 4.2. DMAC Operation and Control Procedure for Software Transfer 4.3. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA)                                                                                                                                                             |                   |

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control 4.2. DMAC Operation and Control Procedure for Software Transfer 4.3. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR)                                                                                                                                                                                                   |                   |

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control 4.2. DMAC Operation and Control Procedure for Software Transfer 4.3. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA)                                                                                                                                                             |                   |

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer & Burst Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control  4. DMAC Control  4.1. Overview of DMAC Control Procedure for Software Transfer 4.2. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.3. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA) 5.4. Configuration B Register (DMACB)                                                                                                                                    |                   |

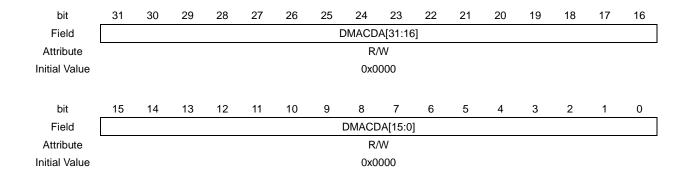

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer & Burst Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control 4.2. DMAC Operation and Control Procedure for Software Transfer 4.3. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA) 5.4. Configuration B Register (DMACB) 5.5. Transfer Source Address Register (DMACSA). 5.6. Transfer Destination Address Register (DMACDA). |                   |

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer & Burst Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control Procedure for Software Transfer 4.2. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA) 5.4. Configuration B Register (DMACB) 5.5. Transfer Source Address Register (DMACDA) 5.6. Transfer Destination Address Register (DMACDA)                                   |                   |

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer & Burst Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control 4.2. DMAC Operation and Control Procedure for Software Transfer 4.3. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA) 5.4. Configuration B Register (DMACB) 5.5. Transfer Source Address Register (DMACSA). 5.6. Transfer Destination Address Register (DMACDA). |                   |

| 3.2. Software-Burst Transfer 3.3. Hardware-Demand Transfer 3.4. Hardware-Block Transfer & Burst Transfer 3.5. Channel Priority Control 4. DMAC Control 4.1. Overview of DMAC Control Procedure for Software Transfer 4.2. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer 5. Registers of DMAC 5.1. List of Registers 5.2. Entire DMAC Configuration Register (DMACR) 5.3. Configuration A Register (DMACA) 5.4. Configuration B Register (DMACB) 5.5. Transfer Source Address Register (DMACSA) 5.6. Transfer Destination Address Register (DMACDA) 6. Usage Precautions  CHAPTER 11: DSTC             |                   |

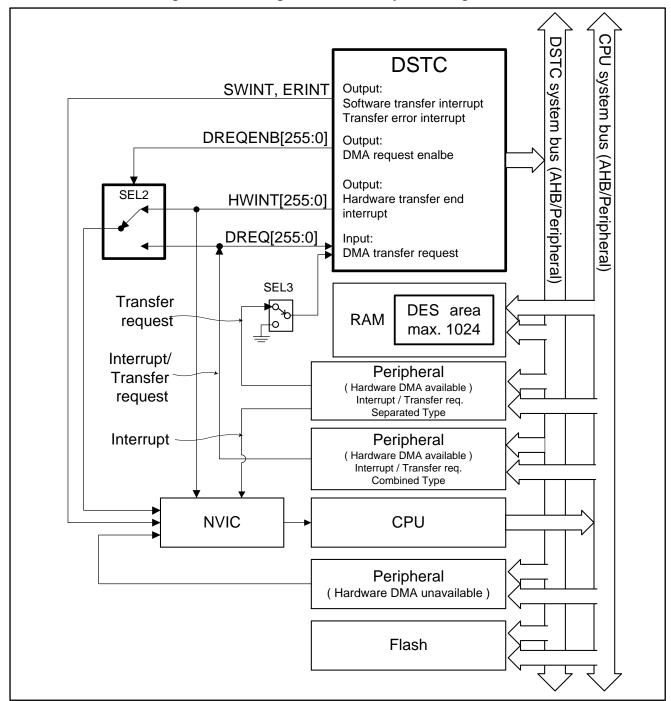

| 3.2. Software-Burst Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

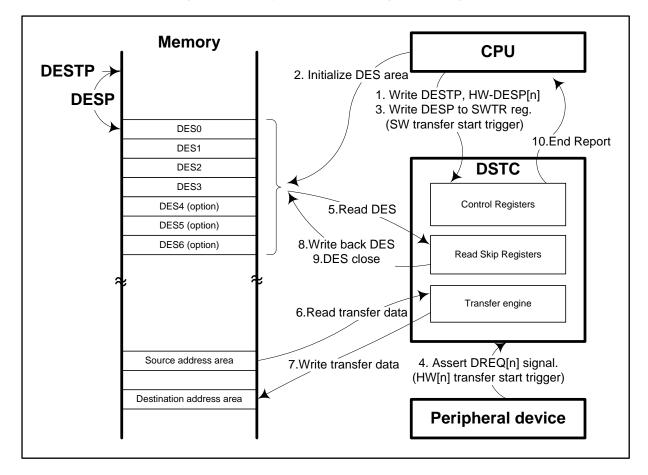

|     | 3. Functions and Operations of DSTC                      | 512 |

|-----|----------------------------------------------------------|-----|

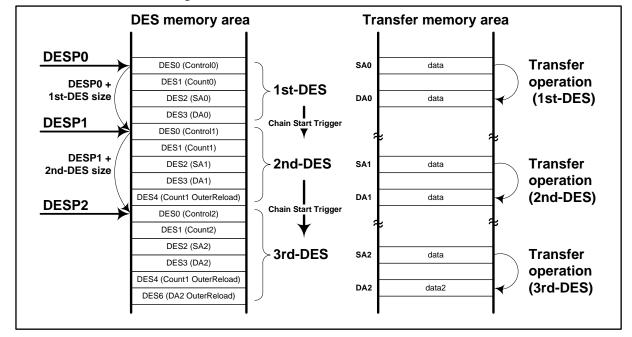

|     | 3.1. Settings of DES                                     | 513 |

|     | 3.1.1. Specifying transfer data size                     | 513 |

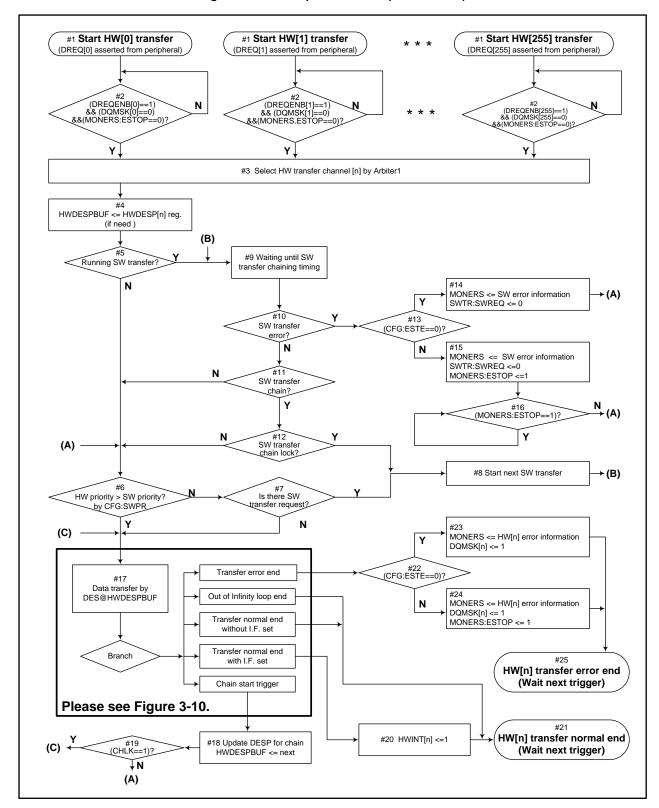

|     | 3.1.2. Setting transfer addresses                        | 514 |

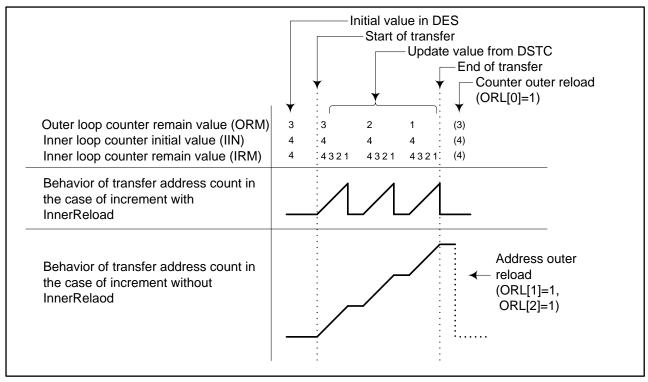

|     | 3.1.3. Specifying OuterReload                            | 516 |

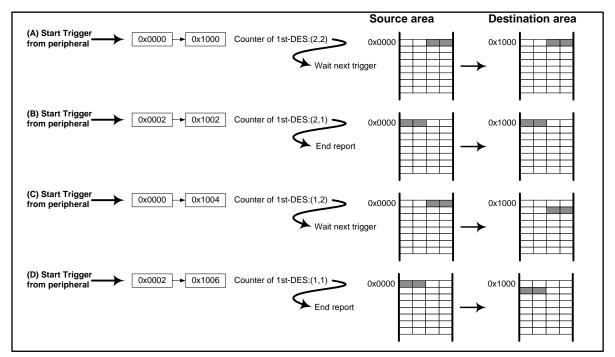

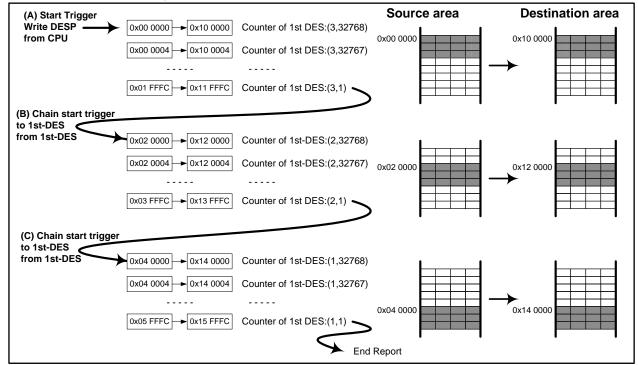

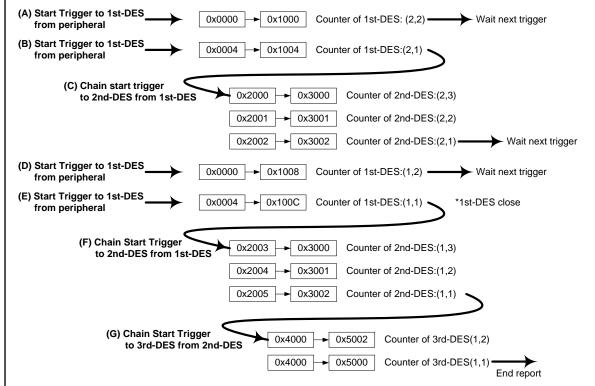

|     | 3.1.4. Setting Chain Start and transfer end notification | 519 |

|     | 3.1.5. Other DES settings                                | 521 |

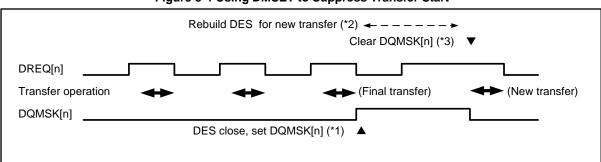

|     | 3.2. Control Functions of DSTC                           |     |

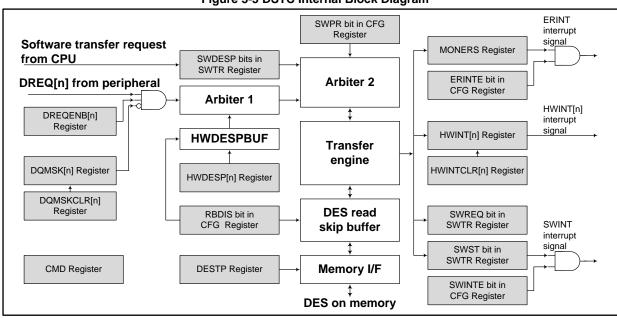

|     | 3.2.1. DSTC internal block diagram                       |     |

|     | 3.2.2. DESTP Register                                    |     |

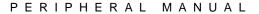

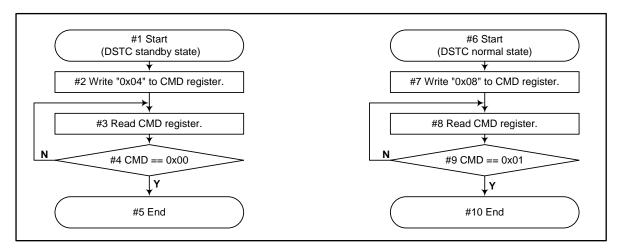

|     | 3.2.3. Control of SW Transfer                            |     |

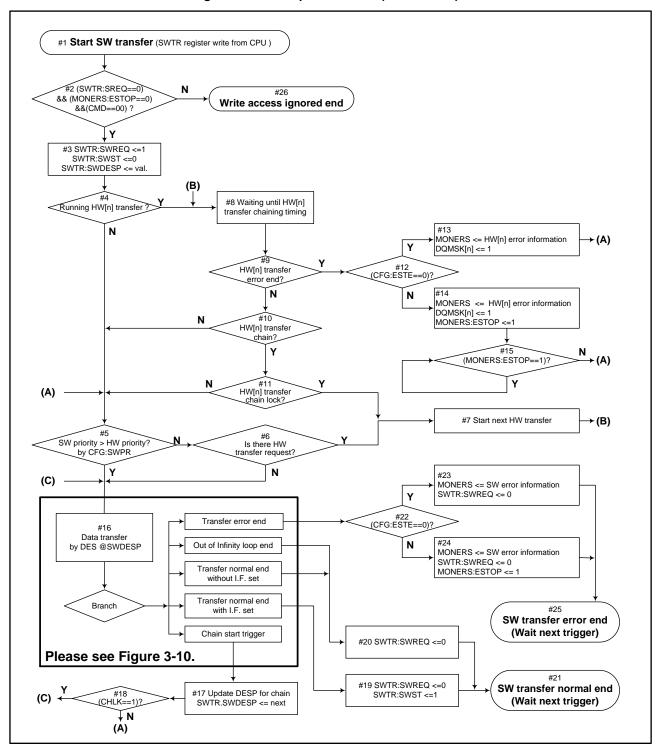

|     | 3.2.4. Control of HW Transfer                            |     |

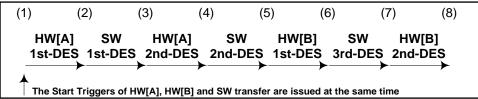

|     | 3.2.5. Arbitration of transfer requests                  |     |