32-BIT MICROCONTROLLER FM4 Family Timer Part CYPRESS<sup>®</sup> PERFORM

PERIPHERAL MANUAL

For the information for microcontroller supports, see the following web site.

http://www.spansion.com/support/microcontrollers/

### Preface

Thank you for your continued use of Cypress products. Read this manual and "Data Sheet" thoroughly before using products in this family.

#### **Purpose of This Manual and Intended Readers**

This manual explains the functions and operations of this family and describes how it is used. The manual is intended for engineers engaged in the actual development of products using this family. For the descriptions on Analog macro, Timer, and Communication Macro, see the respective separate peripheral manual.

#### Note:

This manual explains the configuration and operation of the peripheral functions, but does not cover the specifics of each device in the series.

Users should refer to the respective data sheets of devices for device-specific details.

#### Trademark

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

#### **Sample Programs and Development Environment**

Cypress offers sample programs free of charge for using the peripheral functions of the FM4 family. Cypress also makes available descriptions of the development environment required for this family. Feel free to use them to verify the operational specifications and usage of this Cypress microcontroller.

#### **Microcontroller Support Information:**

http://www.spansion.com/support/microcontrollers/

Note:

Note that the sample programs are subject to change without notice. Since they are offered as a way to demonstrate standard operations and usage, evaluate them sufficiently before running them on your system.

Cypress assumes no responsibility for any damage that may occur as a result of using a sample program.

#### **Overall Organization of This Manual**

Peripheral Manual Timer part has 8 chapters and Appendixes as shown below.

CHAPTER 1: Watchdog Timer CHAPTER 2: Dual Timer CHAPTER 3-1: Watch Counter Prescaler CHAPTER 3-2: Watch Counter CHAPTER 4-1: Real-time Clock CHAPTER 4-2: RTC Count Block (A) CHAPTER 4-3: RTC Count Block (B) CHAPTER 4-3: RTC Clock Control Block (A) CHAPTER 4-5: RTC Clock Control Block (A) CHAPTER 4-6: RTC Clock Control Block (B) CHAPTER 4-7: RTC Clock Control Block (C) CHAPTER 5-1: Base Timer I/O Select Function

CHAPTER 5-2: Base Timer CHAPTER 6: Multifunction Timer CHAPTER 7-1: PPG Configuration CHAPTER 7-2: PPG CHAPTER 8-1: Quadrature Position/Revolution Counter CHAPTER 8-2: Quad Counter Position Rotation Count Display Function Appendixes

### **Related Manuals**

The manuals related to this family are listed below. See the manual appropriate to the applicable conditions.

The contents of these manuals are subject to change without notice. Contact us to check the latest versions available.

#### **Peripheral Manual**

- FM4 Family Peripheral Manual (MN709-00001) Called Peripheral Manual hereafter

- FM4 Family Peripheral Manual Timer Part (this manual) Called Timer Part hereafter

- FM4 Family Peripheral Manual Analog Macro Part (MN709-00003) Called Analog Macro Part hereafter

- FM4 Family Peripheral Manual Communication Macro Part (MN709-00004) Called Communication Macro Part hereafter

- FM4 Family Peripheral Manual GDC Part (MN709-00014) Called GDC Part hereafter

#### **Data Sheet**

For details about device-specific, electrical characteristics, package dimensions, ordering information etc., see the following document.

32-bit Microcontroller FM4 Family Data Sheet

Note:

The data sheets for each series are provided.

See the appropriate data sheet for the series that you are using.

#### **CPU Programming Manual**

For details about ARM Cortex-M4F core, see the following documents that can be obtained from http://www.arm.com/.

- Cortex-M4 Technical Reference Manual

- ARMv7-M Architecture Application Level Reference Manual

#### **Flash Programming Manual**

For details about the functions and operations of the built-in flash memory, see the following document.

■ FM4 Family Flash Programming Manual

Note:

Flash programming manuals for each series are provided.

See the appropriate flash programming manual for the series that you are using.

# How to Use This Manual

#### **Finding a Function**

The following methods can be used to search for the explanation of a desired function in this manual:

Search from the table of the contents

The table of the contents lists the manual contents in the order of description.

Search from the register

The address where each register is located is not described in the text. To verify the address of a register, see A. Register Map in Appendixes.

#### About the Chapters

Basically, this manual explains 1 peripheral function per chapter.

#### Terminology

This manual uses the following terminology.

| Term      | Explanation                           |

|-----------|---------------------------------------|

| Word      | Indicates access in units of 32 bits. |

| Half word | Indicates access in units of 16 bits. |

| Byte      | Indicates access in units of 8 bits.  |

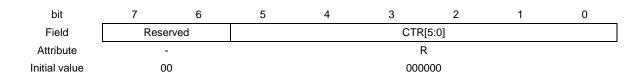

#### Notations

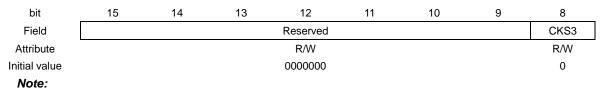

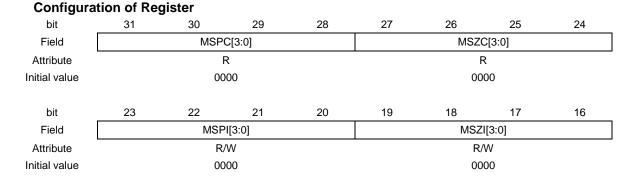

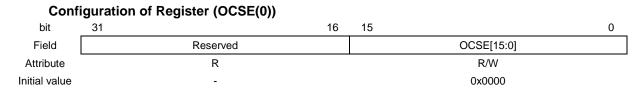

The notations in bit configuration of the register explanation of this manual are written as follows.

- bit: bit number

- Field: bit field name

- Attribute: Attributes for read and write of each bit

- R: Read only

- W: Write only

- R/W: Readable/Writable

- -: Undefined

- Initial value: Initial value of the register after reset

- 0: Initial value is 0

- 1: Initial value is 1

- X: Initial value is undefined

- The multiple bits are written as follows in this manual. Example : bit7:0 indicates the bits from bit7 to bit0

- The values such as for addresses are written as follows in this manual.

| <ul> <li>Hexadecimal number:</li> </ul> | 0x is attached in the beginning of a value as a prefix (example : 0xFFFF) |

|-----------------------------------------|---------------------------------------------------------------------------|

| <ul> <li>Binary number:</li> </ul>      | 0b is attached in the beginning of a value as a prefix (example: 0b1111)  |

| <ul> <li>Decimal number :</li> </ul>    | Written using numbers only (example: 1000)                                |

#### The Target Products in This Manual

In this manual, the products are classified into the following groups and are described follows. For the descriptions such as "TYPE1-M4", see the relevant items of the target product in the list below.

| Description in |                                                   | Flash memory size                   |                                     |

|----------------|---------------------------------------------------|-------------------------------------|-------------------------------------|

| this manual    | 1024 Kbytes                                       | 768 Kbytes                          | 512 Kbytes                          |

|                | MB9BF568M<br>MB9BF568N<br>MB9BF568R<br>MB9BF568RF | MB9BF567M<br>MB9BF567N<br>MB9BF567R | MB9BF566M<br>MB9BF566N<br>MB9BF566R |

| TYPE1-M4       | MB9BF468M<br>MB9BF468N<br>MB9BF468R               | MB9BF467M<br>MB9BF467N<br>MB9BF467R | MB9BF466M<br>MB9BF466N<br>MB9BF466R |

|                | MB9BF368M<br>MB9BF368N<br>MB9BF368R               | MB9BF367M<br>MB9BF367N<br>MB9BF367R | MB9BF366M<br>MB9BF366N<br>MB9BF366R |

|                | MB9BF168M<br>MB9BF168N<br>MB9BF168R               | MB9BF167M<br>MB9BF167N<br>MB9BF167R | MB9BF166M<br>MB9BF166N<br>MB9BF166R |

#### Table 1 TYPE1-M4 Product List

#### Table 2 TYPE2-M4 Product List

| Description in | Flash memory size |            |            |

|----------------|-------------------|------------|------------|

| this manual    | 512 Kbytes        | 384 Kbytes | 256 Kbytes |

|                | MB9BF566K         | MB9BF565K  | MB9BF564K  |

|                | MB9BF566L         | MB9BF565L  | MB9BF564L  |

|                | MB9BF466K         | MB9BF465K  | MB9BF464K  |

| TYPE2-M4       | MB9BF466L         | MB9BF465L  | MB9BF464L  |

|                | MB9BF366K         | MB9BF365K  | MB9BF364K  |

|                | MB9BF366L         | MB9BF365L  | MB9BF364L  |

|                | MB9BF166K         | MB9BF165K  | MB9BF164K  |

|                | MB9BF166L         | MB9BF165L  | MB9BF164L  |

#### Table 3 TYPE3-M4 Product List

| Description       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Flash memory size                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No-Flash                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| in this<br>manual | 2 Mbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.5 Mbytes                                                           | 1 Mbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SRAM size<br>256 Kbytes          |

| in this           | 2 Mbytes           S6E2CCA L0AGL20           S6E2CCA LHAGL20           S6E2CCA LHAGL20           S6E2CCAJOAGV20           S6E2CCAJHAGV20           S6E2CCAJHAGV20           S6E2CCAJHAGV20           S6E2CCAJAGB10           S6E2CCAJAGB10           S6E2CCAJAGB10           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGB10           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CCAJGAGV20           S6E2CSAL0AGL20           S6E2C4AL0AGV20           S6E2C4AJ0AGV20           S6E2C4AL0AGL20           S6E2C3AL0AGL20           S6E2C3AL0AGL20           S6E2C3AL0AGL20           S6E2C3AL0AGL20           S6E2C3AL0AGL20           S6E2C2AL0AGV20           S6E2C2AL0AGV20           S6E2C2AL0AGV20           S6E2C2AJHAGV20           S6E2C2AJHAGV20           S6E2C2AJHAGV20           S6E2C2AJHAGV20 |                                                                      | 1 Mbytes           S6E2CC8 L0AGL20           S6E2CC8 LHAGL20           S6E2CC8 LHAGL20           S6E2CC8J0AGV20           S6E2CC8J0AGV20           S6E2CC8J0AGV20           S6E2CC8J0AGB10           S6E2CC8J0AGB10           S6E2CC8J0AGV20           S6E2CC8J0AGB10           S6E2CC8JHAGB10           S6E2CC8JHAGV20           S6E2CC8JGAGB10           S6E2CC8JGAGB10           S6E2CC8JGAGB10           S6E2CC8JOAGV20           S6E2CC8JOAGV20           S6E2C58J0AGV20           S6E2C58J0AGV20           S6E2C58J0AGV20           S6E2C48L0AGL20           S6E2C48J0AGV20           S6E2C48J0AGV20           S6E2C48J0AGV20           S6E2C38L0AGL20           S6E2C38J0AGV20           S6E2C38J0AGV20           S6E2C38J0AGV20           S6E2C38J0AGV20           S6E2C28L0AGL20           S6E2C28J0AGV20           S6E2C28JHAGV20           S6E2C28JHAGV20           S6E2C28JHAGV20           S6E2C28JHAGV20           S6E2C28JHAGV20           S6E2C28JHAGP20           S6E2C28JHAGV20           S6E2C28JHAGV20 <tr< td=""><td>SRAM size</td></tr<> | SRAM size                        |

| -                 | S6E2C2AH0AGV20<br>S6E2C2AHHAGV20<br>S6E2C1AL0AGL20<br>S6E2C1AJ0AGV20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S6E2C29H0AGV20<br>S6E2C29HHAGV20<br>S6E2C19L0AGL20<br>S6E2C19J0AGV20 | S6E2C28H0AGV20<br>S6E2C28HHAGV20<br>S6E2C18L0AGL20<br>S6E2C18J0AGV20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S6E2C10H2AGV20<br>S6E2C10J2AGV20 |

|                   | S6E2C1AJ0AGB10<br>S6E2C1AH0AGV20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S6E2C19J0AGB10<br>S6E2C19H0AGV20                                     | S6E2C18J0AGB10<br>S6E2C18H0AGV20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S6E2C10J2AGB10<br>S6E2C10L2AGL20 |

|                     | Flash memory s  | ize 384 Kbytes  |  |

|---------------------|-----------------|-----------------|--|

| Description in this |                 | VRAM 512 Kbytes |  |

| manual              | VRAM 512 Kbytes | +               |  |

|                     |                 | VFLASH 2 Mbytes |  |

|                     | S6E2D35G0AGB30  |                 |  |

|                     | S6E2D35G0AGV20  | S6E2D35GJAMV20  |  |

|                     | S6E2D35G0AGE20  | S0E2D35GJANIV20 |  |

|                     | S6E2D35J0AGV20  |                 |  |

|                     | S6E2D55G0AGB30  |                 |  |

|                     | S6E2D55G0AGV20  | S6E2D55GJAMV20  |  |

|                     | S6E2D55G0AGE20  | S0E2DSSGJANIV20 |  |

| TYPF4-M4            | S6E2D55J0AGV20  |                 |  |

| 11924-1014          | S6E2DF5G0AGB30  |                 |  |

|                     | S6E2DF5G0AGV20  | S6E2DF5GJAMV20  |  |

|                     | S6E2DF5G0AGE20  | S0E2DF5GJAWV20  |  |

|                     | S6E2DF5J0AGV20  |                 |  |

|                     | S6E2DH5G0AGB30  |                 |  |

|                     | S6E2DH5G0AGV20  |                 |  |

|                     | S6E2DH5G0AGE20  | S6E2DH5GJAMV20  |  |

|                     | S6E2DH5J0AGV20  |                 |  |

#### Table 4 TYPE4-M4 Product List

| Description in | Flash memory size |                |  |

|----------------|-------------------|----------------|--|

| this manual    | 1 Mbytes          | 512 Kbytes     |  |

|                | S6E2GM8JHAGV20    | S6E2GM6JHAGV20 |  |

|                | S6E2GM8J0AGV20    | S6E2GM6J0AGV20 |  |

|                | S6E2GM8HHAGV20    | S6E2GM6HHAGV20 |  |

|                | S6E2GM8H0AGV20    | S6E2GM6H0AGV20 |  |

|                | S6E2GK8JHAGV20    | S6E2GK6JHAGV20 |  |

|                | S6E2GK8J0AGV20    | S6E2GK6J0AGV20 |  |

|                | S6E2GK8HHAGV20    | S6E2GK6HHAGV20 |  |

|                | S6E2GK8H0AGV20    | S6E2GK6H0AGV20 |  |

| TYPE5-M4       | S6E2GH8J0AGV20    | S6E2GH6J0AGV20 |  |

|                | S6E2GH8H0AGV20    | S6E2GH6H0AGV20 |  |

|                | S6E2G28JHAGV20    | S6E2G26JHAGV20 |  |

|                | S6E2G28J0AGV20    | S6E2G26J0AGV20 |  |

|                | S6E2G28HHAGV20    | S6E2G26H0AGV20 |  |

|                | S6E2G28H0AGV20    | S6E2G26HHAGV20 |  |

|                | S6E2G38J0AGV20    | S6E2G36J0AGV20 |  |

|                | S6E2G38H0AGV20    | S6E2G36H0AGV20 |  |

#### Table 5 TYPE5-M4 Product List

| Description in | Flash memory size |                |  |

|----------------|-------------------|----------------|--|

| this manual    | 512 Kbytes        | 256 Kbytes     |  |

|                | S6E2HG6G0AGV20    | S6E2HG4G0AGV20 |  |

|                | S6E2HG6F0AGV20    | S6E2HG4F0AGV20 |  |

|                | S6E2HG6E0AGV20    | S6E2HG4E0AGV20 |  |

|                | S6E2HG6G0AGB10    | S6E2HG4G0AGB10 |  |

|                | S6E2HE6G0AGV20    | S6E2HE4G0AGV20 |  |

|                | S6E2HE6F0AGV20    | S6E2HE4F0AGV20 |  |

|                | S6E2HE6E0AGV20    | S6E2HE4E0AGV20 |  |

| TYPE6-M4       | S6E2HE6G0AGB10    | S6E2HE4G0AGB10 |  |

| 1 Y PE6-1014   | S6E2H46G0AGV20    | S6E2H44G0AGV20 |  |

|                | S6E2H46F0AGV20    | S6E2H44F0AGV20 |  |

|                | S6E2H46E0AGV20    | S6E2H44E0AGV20 |  |

|                | S6E2H46G0AGB10    | S6E2H44G0AGB10 |  |

|                | S6E2H16G0AGV20    | S6E2H14G0AGV20 |  |

|                | S6E2H16F0AGV20    | S6E2H14F0AGV20 |  |

|                | S6E2H16E0AGV20    | S6E2H14E0AGV20 |  |

|                | S6E2H16G0AGB10    | S6E2H14G0AGB10 |  |

#### Table 6 TYPE6-M4 Product List

# **Table of Contents**

| CHAPTER 1: Watchdog Timer                                                              |    |

|----------------------------------------------------------------------------------------|----|

| 1. Overview                                                                            |    |

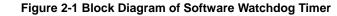

| 2. Configuration and Block Diagram                                                     |    |

| 3. Operations                                                                          |    |

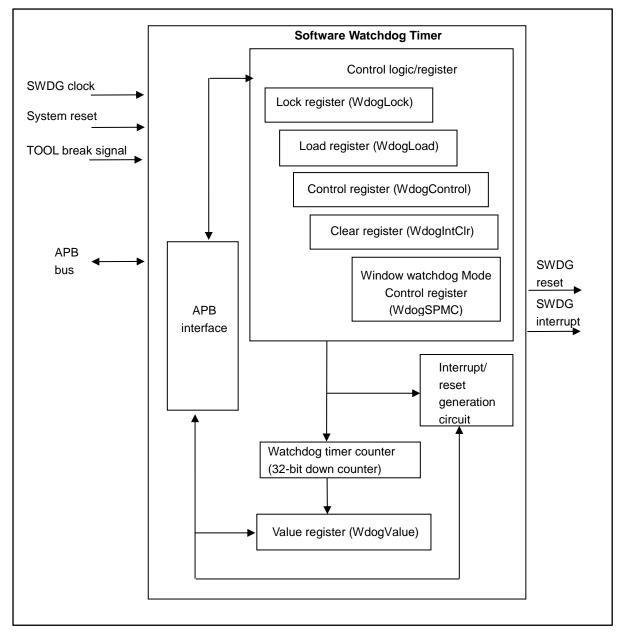

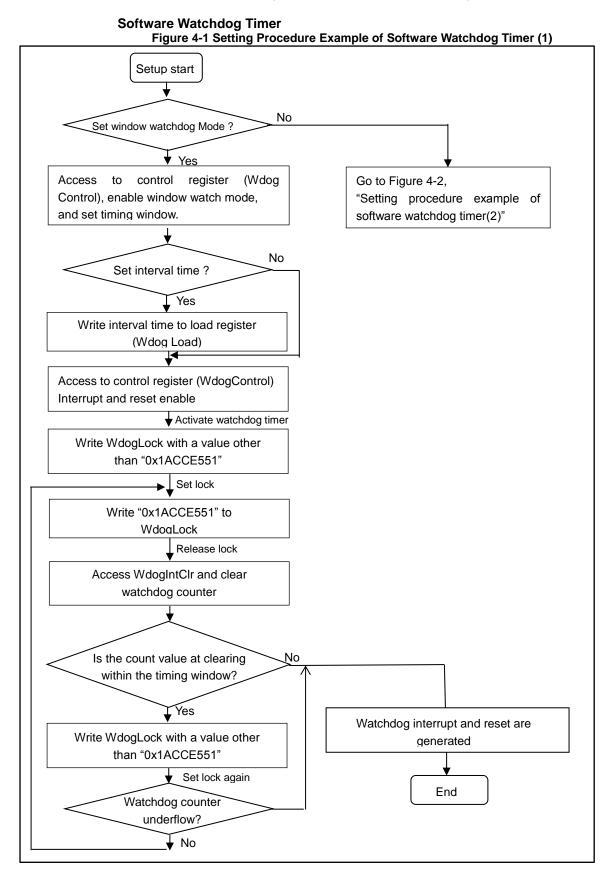

| 4. Setting Procedure Example                                                           |    |

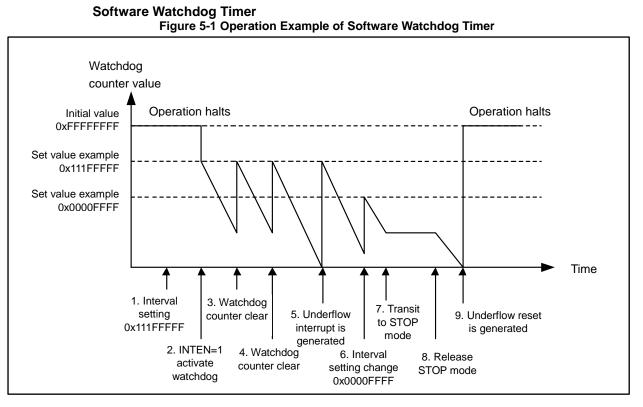

| 5. Operation Example                                                                   | 34 |

| 6. Registers                                                                           |    |

| 6.1. Software Watchdog Timer Load Register (WdogLoad)                                  |    |

| 6.2. Software Watchdog Timer Value Register (WdogValue)                                |    |

| 6.3. Software Watchdog Timer Control Register (WdogControl)                            |    |

| 6.4. Software Watchdog Timer Clear Register (WdogIntClr)                               | 42 |

| 6.5. Software Watchdog Timer Interrupt Status Register (WdogRIS)                       | 43 |

| 6.6. Software Watchdog Timer Window Watchdog Mode Control Register (WdogSPMC)          |    |

| 6.7. Software Watchdog Timer Lock Register (WdogLock)                                  |    |

| 6.8. Hardware Watchdog Timer Load Register (WDG_LDR)                                   |    |

| 6.9. Hardware Watchdog Timer Value Register (WDG_VLR)                                  |    |

| 6.10. Hardware Watchdog Timer Control Register (WDG_CTL)                               | 48 |

| 6.11. Hardware Watchdog Timer Clear Register (WDG_ICL)                                 |    |

| 6.12. Hardware Watchdog Timer Interrupt Status Register (WDG_RIS)                      |    |

| 6.13. Hardware Watchdog Timer Lock Register (WDG_LCK)                                  |    |

| 7. Usage Precautions                                                                   |    |

| CHAPTER 2: Dual Timer                                                                  |    |

| 1. Overview                                                                            |    |

| 2. Configuration                                                                       |    |

| 3. Operations                                                                          |    |

| 3.1. Timer Operating Mode                                                              |    |

| 3.2. Initial State                                                                     |    |

| 3.3. Interrupt Operation                                                               |    |

| 4. Setting Procedure Example                                                           |    |

| 5. Registers                                                                           |    |

| 5.1. Load Register (TimerXLoad) X=1 or 2                                               |    |

| 5.2. Value Register (TimerXValue) X=1 or 2                                             |    |

| 5.3. Control Register (TimerXControl) X=1 or 2                                         |    |

| 5.4. Interrupt Clear Register (TimerXIntClr) X=1 or 2                                  |    |

| 5.5. Interrupt Status Register (TimerXRIS) X=1 or 2                                    |    |

| 5.6. Masked Interrupt Status Register (TimerXMIS) X=1 or 2                             |    |

| 5.7. Background Load Register (TimerXBGLoad) X=1 or 2                                  |    |

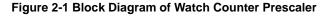

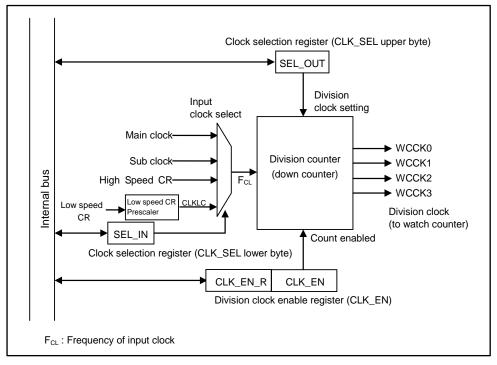

| CHAPTER 3-1: Watch Counter Prescaler                                                   |    |

| 1. Overview of Watch Counter Prescaler                                                 | -  |

| 2. Configuration of Watch Counter Prescaler                                            |    |

| 3. Explanation of Operations and Setting Procedure Examples of Watch Counter Prescaler |    |

| 4. Registers of Watch Counter Prescaler                                                |    |

| 4.1. Clock Selection Register (CLK_SEL)                                                |    |

| 4.2. Division Clock Enable Register (CLK_EN)                                           |    |

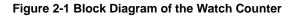

| CHAPTER 3-2: Watch Counter                                                             |    |

| 1. Overview of the Watch Counter                                                       |    |

| 2. Configuration of the Watch Counter                                                  |    |

| 3. Interrupts of the Watch Counter                                                     |    |

| 4. Explanation of Operations and Setting Procedure Examples of the Watch Counter       |    |

| 5. Registers of Watch Counter                                                          |    |

| 5.1. Watch Counter Read Register (WCRD)                                                |    |

| 5.2. Watch Counter Reload Register (WCRL)                                              |    |

| 5.3. Watch Counter Control Register (WCCR)                                             |    |

| CHAPTER 4-1: Real-time Clock                                                           |    |

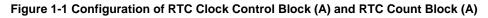

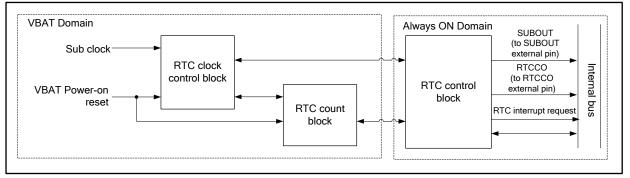

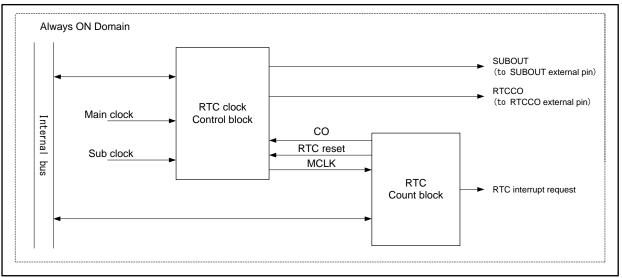

| 1. Configuration of Real-time Clock                                                    |    |

| 2. Real-time Clock Acronym                                                             | 98 |

| 3. Resetting RTC                                                         | 99    |

|--------------------------------------------------------------------------|-------|

| CHAPTER 4-2: RTC Count Block (A)                                         | . 101 |

| 1. Overview of RTC Count Block                                           | 102   |

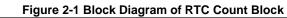

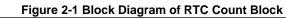

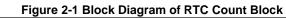

| 2. Block Diagram of RTC Count Block                                      | . 103 |

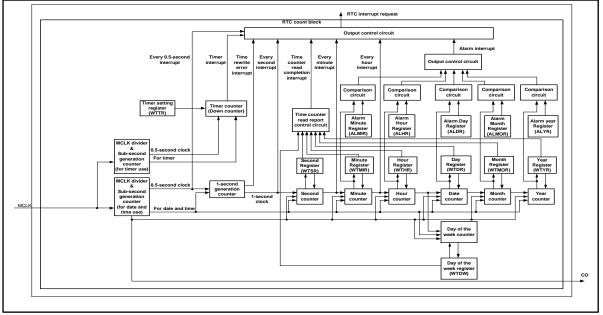

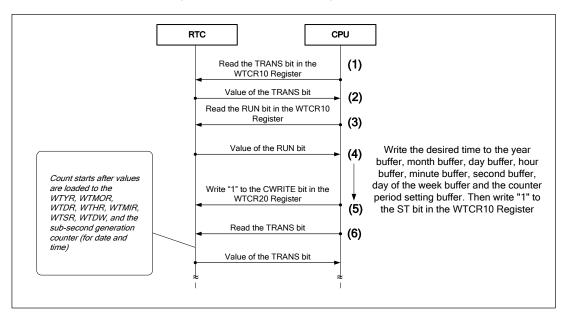

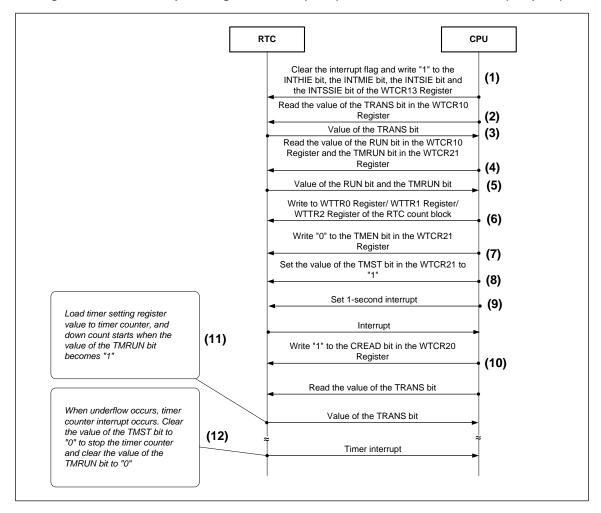

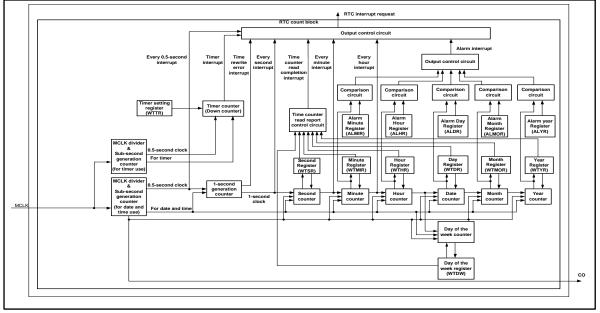

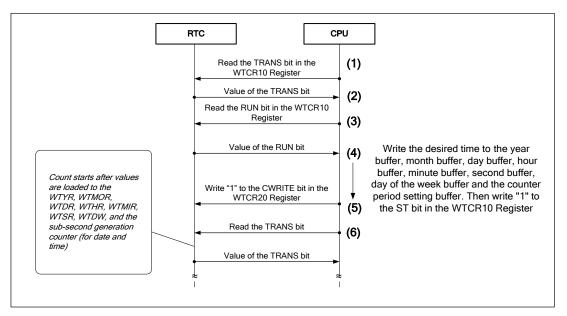

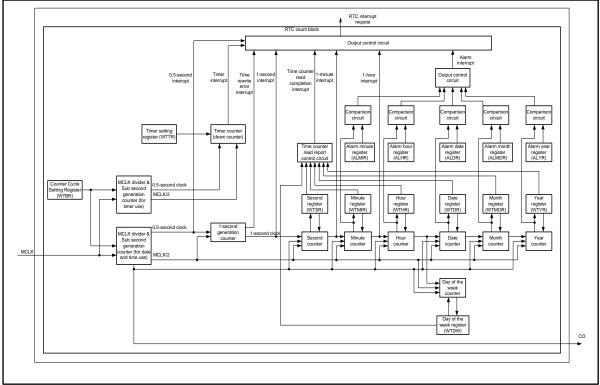

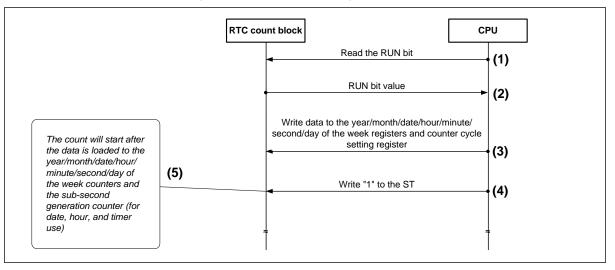

| 3. Operations of RTC Count Block and Setting Procedures Examples         | . 105 |

| 4. RTC Control Block Reset Operation                                     | . 118 |

| 5. Leap Year Compliance of RTC Count Block                               | . 121 |

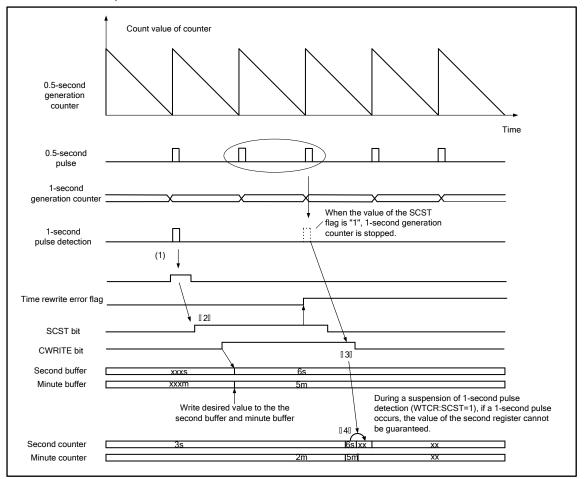

| 6. Time Rewrite Error                                                    | . 123 |

| 7. Registers in RTC Control Block                                        |       |

| 7.1. Control Register 10 (WTCR 10)                                       |       |

| 7.2. Control Register 11 (WTCR 11)                                       |       |

| 7.3. Control Register 12 (WTCR 12)                                       | . 129 |

| 7.4. Control Register 13 (WTCR 13)                                       |       |

| 7.5. Control Register 20 (WTCR 20)                                       | . 134 |

| 7.6. Control Register 21 (WTCR 21)                                       |       |

| 7.7. Second Register (WTSR)                                              |       |

| 7.8. Minute Register (WRMIR)                                             |       |

| 7.9. Hour Register (WTHR)                                                |       |

| 7.10. Day Register (WTDR)                                                |       |

| 7.11. Day of the Week Register (WTDW)                                    |       |

| 7.12. Month Register (WTMOR)                                             |       |

| 7.13. Year Register (WTYR)                                               |       |

| 7.14. Alarm Minute Register (ALMIR)                                      |       |

| 7.15. Alarm Hour Register (ALHR)                                         |       |

| 7.16. Alarm Day Register (ALDR)                                          |       |

| 7.17. Alarm Month Register (ALMOR)                                       |       |

| 7.18. Alarm Year Register (ALYR)                                         |       |

| 7.19. Time Setting Register 0 (WTTR0)                                    |       |

| 7.20. Time Setting Register 1 (WTTR1)                                    |       |

| 7.21. Time Setting Register 2 (WTTR2)                                    |       |

| 8. Usage Precautions                                                     |       |

| CHAPTER 4-3: RTC Count Block (B)                                         |       |

| 1. Overview of RTC Count Block                                           |       |

| 2. Block Diagram of RTC Count Block                                      |       |

| 3. Operations of RTC Count Block and Setting Procedures Examples         |       |

| 4. RTC Control Block Reset Operation                                     |       |

| 5. Leap Year Compliance of RTC Count Block                               |       |

| 6. Time Rewrite Error                                                    |       |

| 7. Registers in RTC Control Block                                        |       |

| 7.1. Control Register 10 (WTCR 10)                                       |       |

| 7.2. Control Register 11 (WTCR 11)                                       |       |

| 7.3. Control Register 12 (WTCR 12)                                       |       |

| 7.4. Control Register 13 (WTCR 13)                                       |       |

| 7.5. Control Register 20 (WTCR 20)<br>7.6. Control Register 21 (WTCR 21) |       |

| 7.5. Control Register 21 (WTCR 21)                                       |       |

| 7.8. Minute Register (WRMIR)                                             |       |

| 7.9. Hour Register (WTHR)                                                |       |

| 7.9. Tour Register (WTDR)                                                |       |

| 7.10. Day Register (WTDR)                                                |       |

| 7.11. Day of the week Register (WTDW)                                    |       |

| 7.12. Month Register (WTMOR)                                             |       |

| 7.13. Teal Register (WTTR)                                               |       |

| 7.14. Alarm Hour Register (ALHR)                                         |       |

| 7.16. Alarm Day Register (ALDR)                                          |       |

| 7.17. Alarm Month Register (ALMOR)                                       |       |

| 7.18. Alarm Year Register (ALYR)                                         |       |

| J ( )                                                                    |       |

| 7.19. Time Setting Register 0 (WTTR0)                            | 200 |

|------------------------------------------------------------------|-----|

| 7.20. Time Setting Register 1 (WTTR1)                            | 201 |

| 7.21. Time Setting Register 2 (WTTR2)                            | 202 |

| 8. Usage Precautions                                             | 203 |

| CHAPTER 4-4: RTC Count Block (C)                                 | 205 |

| 1. Overview of RTC Count Block                                   | 206 |

| 2. Block Diagram of RTC Count Block                              | 207 |

| 3. Operations of RTC Count Block and Setting Procedures Examples |     |

| 4. RTC Control Block Reset Operation                             |     |

| 5. Leap Year Compliance of RTC Count Block                       | 224 |

| 6. Time Rewrite Error                                            |     |

| 7. Registers in RTC Control Block                                | 228 |

| 7.1. Control Register 1 (WTCR 1)                                 | 229 |

| 7.2. Control Register 2 (WTCR 2)                                 |     |

| 7.3. Counter Cycle Setting Register (WTBR)                       |     |

| 7.4. Day Register (WTDR)                                         |     |

| 7.5. Hour Register (WTHR)                                        |     |

| 7.6. Minute Register (WRMIR)                                     |     |

| 7.7. Second Register (WTSR)                                      |     |

| 7.8. Year Register (WTYR)                                        |     |

| 7.9. Month Register (WTMOR)                                      |     |

| 7.10. Day of the Week Register (WTDW)                            |     |

| 7.11. Alarm Day Register (ALDR)                                  |     |

| 7.12. Alarm Hour Register (ALHR)                                 |     |

| 7.13. Alarm Minute Register (ALMIR)                              |     |

| 7.14. Alarm Year Register (ALYR)                                 |     |

| 7.15. Alarm Month Register (ALMOR)                               |     |

| 7.16. Time Setting Register (WTTR)                               |     |

| 8. Usage Precautions                                             |     |

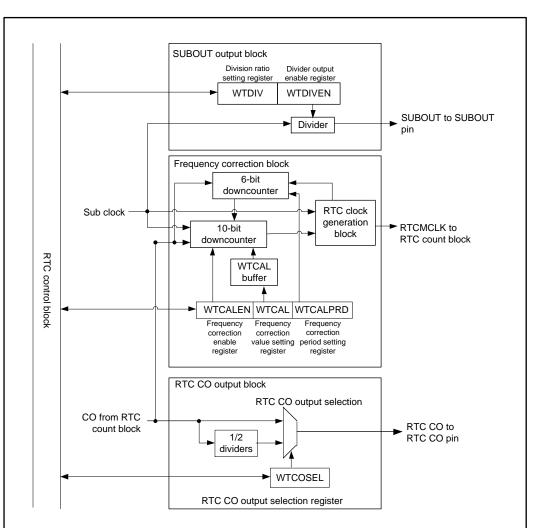

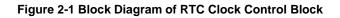

| CHAPTER 4-5: RTC Clock Control Block (A)                         |     |

| 1. Overview of RTC Clock Control Block                           |     |

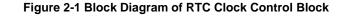

| 2. Configuration of RTC Clock Control Block                      |     |

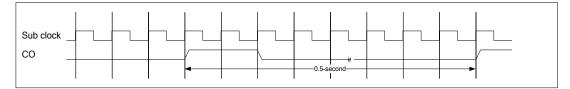

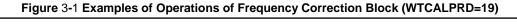

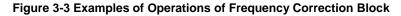

| 3. Operations of RTC Clock Control Block                         | 256 |

| 4. Setting Procedures of RTC Clock Control Block                 | 259 |

| 5. Registers of RTC Clock Control Block                          |     |

| 5.1. Frequency Correction Value Setting Register 0 (WTCAL0)      | 263 |

| 5.2. Frequency Correction Value Setting Register 1 (WTCAL1)      | 264 |

| 5.3. Frequency Correction Enable Register (WTCALEN)              | 265 |

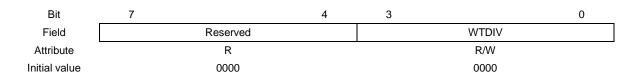

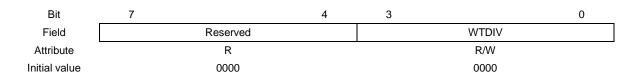

| 5.4. Division Ratio Setting Register (WTDIV)                     | 266 |

| 5.5. Divider Output Enable Register (WTDIVEN)                    | 267 |

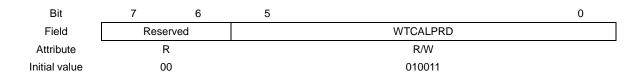

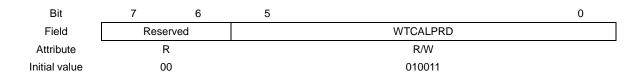

| 5.6. Frequency Correction Period Setting Register (WTCALPRD)     | 268 |

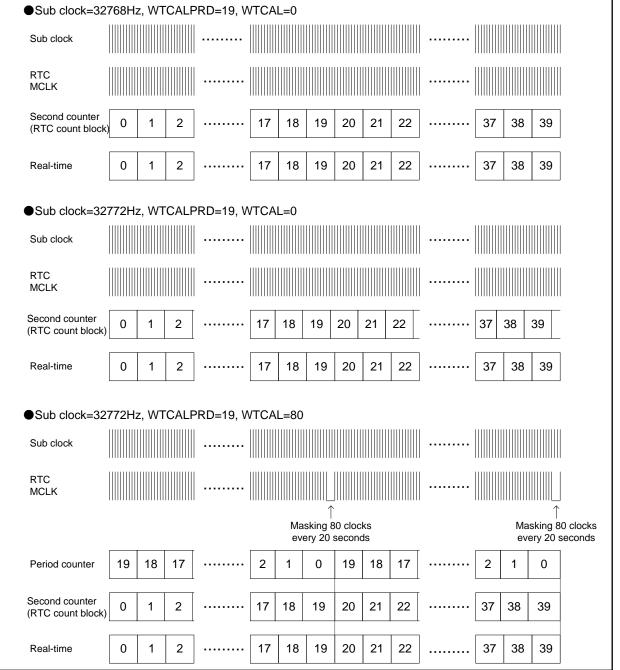

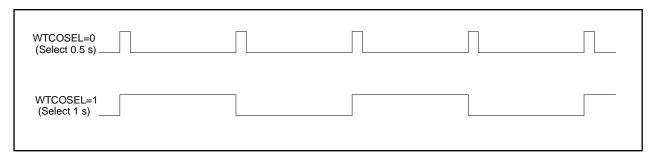

| 5.7. RTCCO Output Selection Register (WTCOSEL)                   | 269 |

| CHAPTER 4-6: RTC Clock Control Block (B)                         | 271 |

| 1. Overview of RTC Clock Control Block                           | 272 |

| 2. Configuration of RTC Clock Control Block                      | 273 |

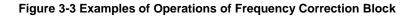

| 3. Operations of RTC Clock Control Block                         | 274 |

| 4. Setting Procedures of RTC Clock Control Block                 | 277 |

| 5. Registers of RTC Clock Control Block                          | 278 |

| 5.1. Frequency Correction Value Setting Register 0 (WTCAL0)      | 279 |

| 5.2. Frequency Correction Value Setting Register 1 (WTCAL1)      |     |

| 5.3. Frequency Correction Enable Register (WTCALEN)              |     |

| 5.4. Division Ratio Setting Register (WTDIV)                     | 282 |

| 5.5. Divider Output Enable Register (WTDIVEN)                    |     |

| 5.6. Frequency Correction Period Setting Register (WTCALPRD)     |     |

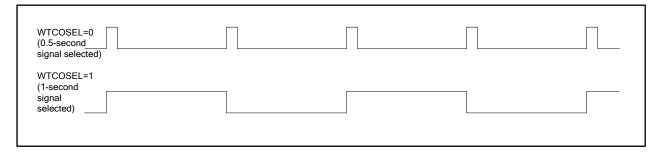

| 5.7. RTCCO Output Selection Register (WTCOSEL)                   |     |

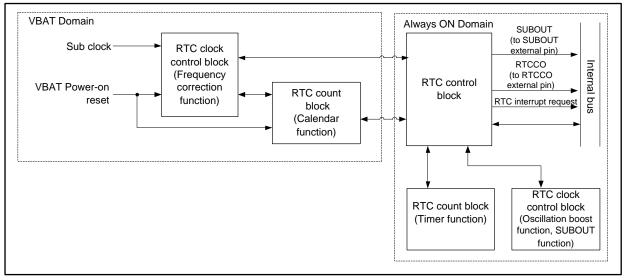

| CHAPTER 4-7: RTC Clock Control Block (C)                         |     |

| 1. Overview of RTC Clock Control Block                           | 288 |

| 2. Configuration of RTC Clock Control Block                                 | 289 |

|-----------------------------------------------------------------------------|-----|

| 3. Operations of RTC Clock Control Block                                    |     |

| 4. Setting Procedures of RTC Clock Control Block                            |     |

| 5. Registers of RTC Clock Control Block                                     |     |

| 5.1. Clock Selection Register (WTCLKS)                                      |     |

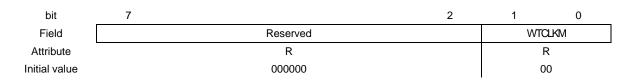

| 5.2. Selection Clock Status Register (WTCLKM)                               |     |

| 5.3. Frequency Correction Value Setting Register (WTCAL)                    |     |

| 5.4. Frequency Correction Enable Register (WTCALEN)                         |     |

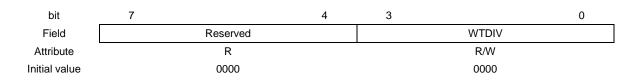

| 5.5. Division Ratio Setting Register (WTDIV)                                |     |

| 5.6. Divider Output Enable Register (WTDIVEN)                               |     |

| 5.7. Frequency Correction Period Setting Register (WTCALPRD)                |     |

| 5.8. RTCCO Output Selection Register (WTCOSEL)                              |     |

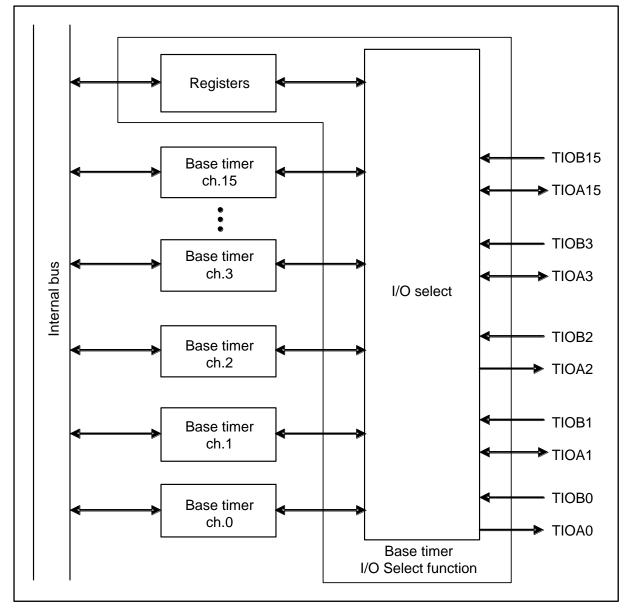

| CHAPTER 5-1: Base Timer I/O Select Function                                 |     |

| 1. Overview                                                                 |     |

| 2. Configuration                                                            |     |

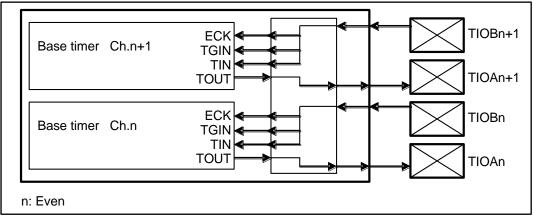

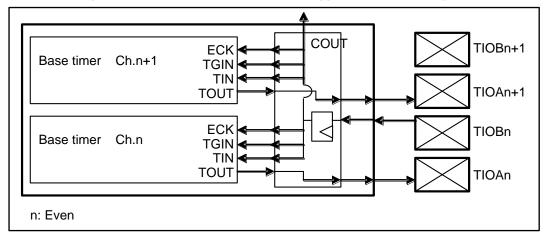

| 3. I/O Mode                                                                 |     |

| 3.1. Pins                                                                   |     |

| 3.2. I/O Mode                                                               | -   |

| 4. Registers                                                                |     |

| 4.1. I/O Select Register (BTSEL0123)                                        |     |

| 4.2. I/O Select Register (BTSEL4567)                                        |     |

| 4.3. I/O Select Register (BTSEL89AB)                                        |     |

| 4.4. I/O Select Register (BTSELCDEF)                                        |     |

| 4.5. Software-based Simultaneous Startup Register (BTSSSR)                  |     |

| CHAPTER 5-2: Base Timer                                                     |     |

| 1. Overview of Base Timer                                                   |     |

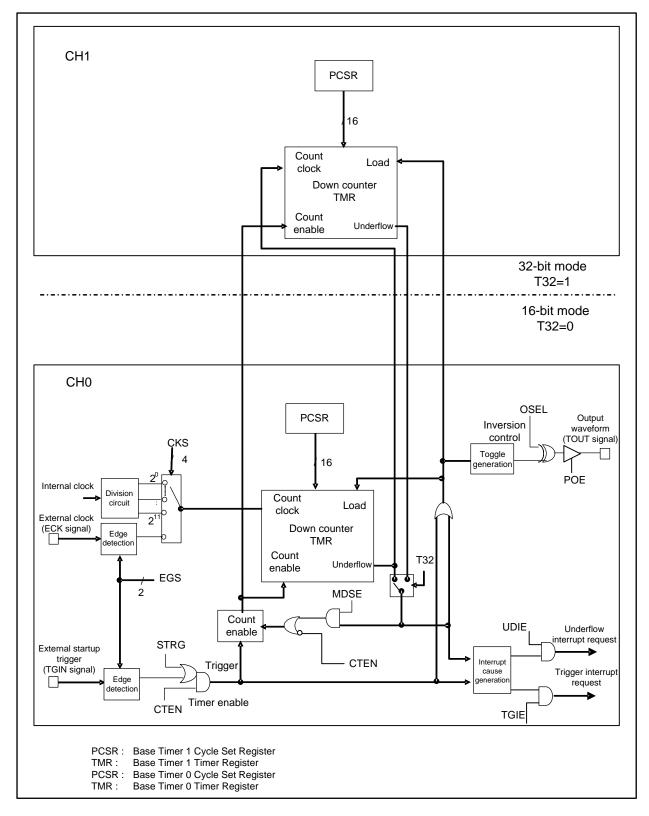

| 2. Block Diagram of Base Timer                                              |     |

| 3. Operations of the Base Timer                                             |     |

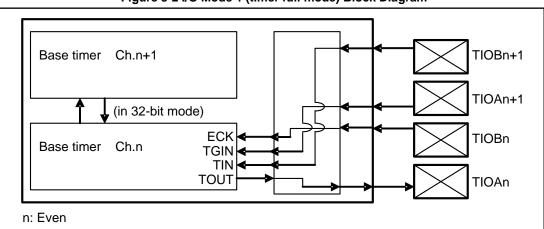

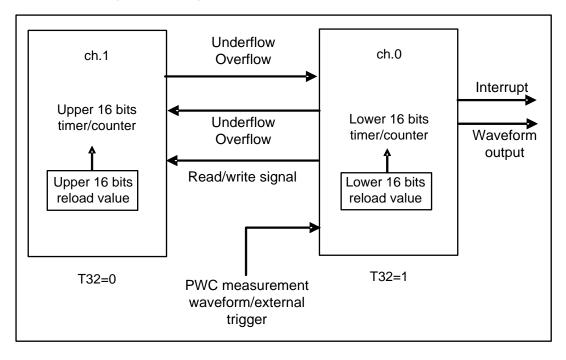

| 4. 32-bit mode operations                                                   |     |

| 5. Base Timer Interrupt                                                     |     |

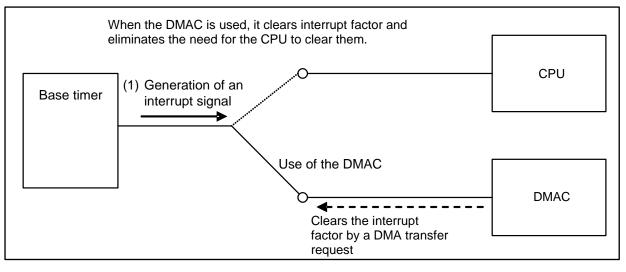

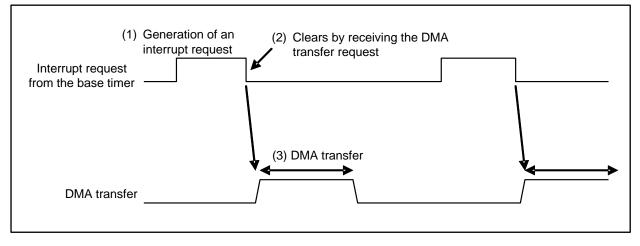

| 6. Starting the DMA Controller (DMAC)                                       |     |

| 7. Registers of Base timer                                                  |     |

| 8. Notes on using the Base Timer.                                           |     |

| 9. Descriptions of Base Timer Functions                                     |     |

| 9.1. PWM Timer Function                                                     |     |

| 9.1.1. 16-bit PWM Timer Operations                                          |     |

| 9.1.2. One-shot Operation                                                   |     |

| 9.1.3. Interrupt Factors and Timing Chart                                   |     |

| 9.1.4. Output Waveforms                                                     |     |

| 9.1.5. PWM Timer Operation Flowchart                                        |     |

| 9.1.6. Timer Control Registers (TMCR and TMCR2) and Status Control Register |     |

| used when the PWM Timer is selected                                         |     |

| 9.1.7. PWM Cycle Set Register (PCSR)                                        |     |

| 9.1.8. PWM Duty Set Register (PDUT)<br>9.1.9. Timer Register (TMR)          |     |

| 9.1.9. Timer Register (TVIR)                                                |     |

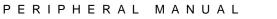

| 9.2. PPG timer function<br>9.2.1. 16-bit PPG Timer Operations               |     |

| 9.2.1. To-bit PPG Timer Operations                                          |     |

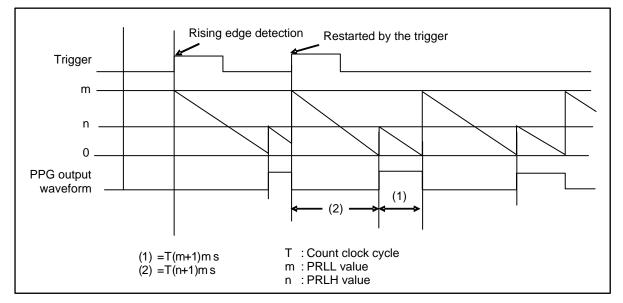

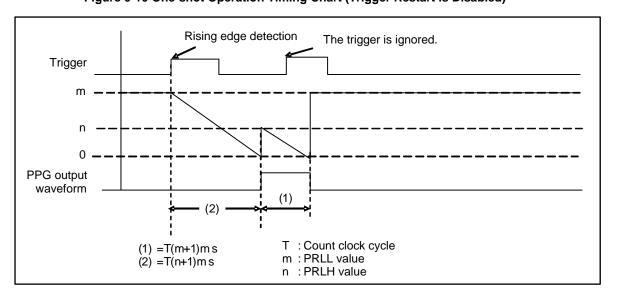

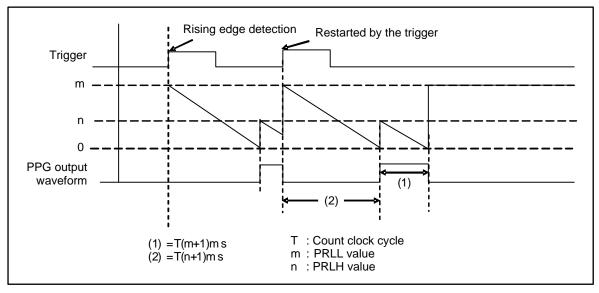

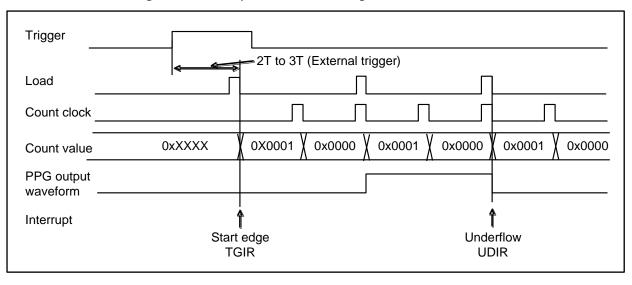

| 9.2.3. One-shot Operation                                                   |     |

| 9.2.4. Interrupt Factors and Timing Chart                                   |     |

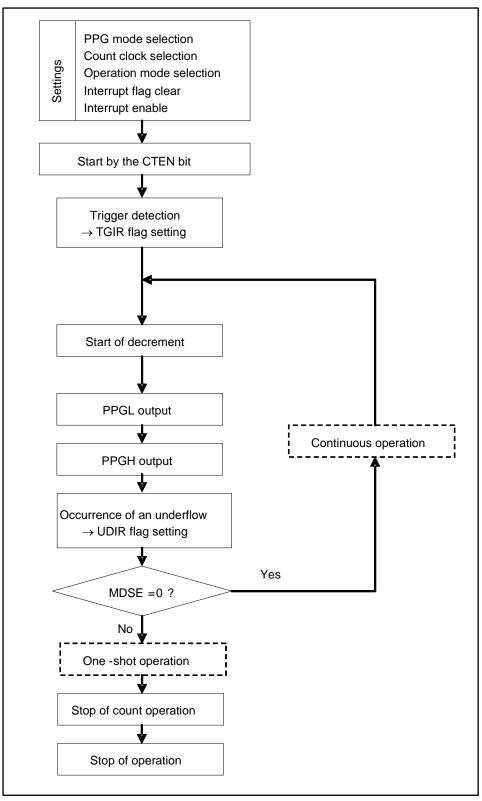

| 9.2.5. PPG Timer Operation Flowchart                                        |     |

| 9.2.6. Timer Control Registers (TMCR and TMCR2) and Status Control Register |     |

| used when the PPG Timer is selected                                         |     |

| 9.2.7. LOW Width Reload Register (PRLL)                                     |     |

|                                                                             |     |

| 9.2.8. HIGH Width Reload Register (PRLH)<br>9.2.9. Timer Register (TMR)     |     |

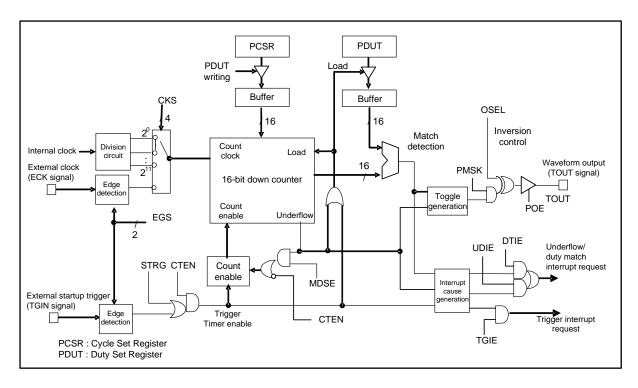

| 9.3. Reload timer function                                                  |     |

| J.J. NEIUAU IIITEI IUIUIUII                                                 | 300 |

| 9.3.1. Operations of the 16-bit Reload Timer                                             | 387     |

|------------------------------------------------------------------------------------------|---------|

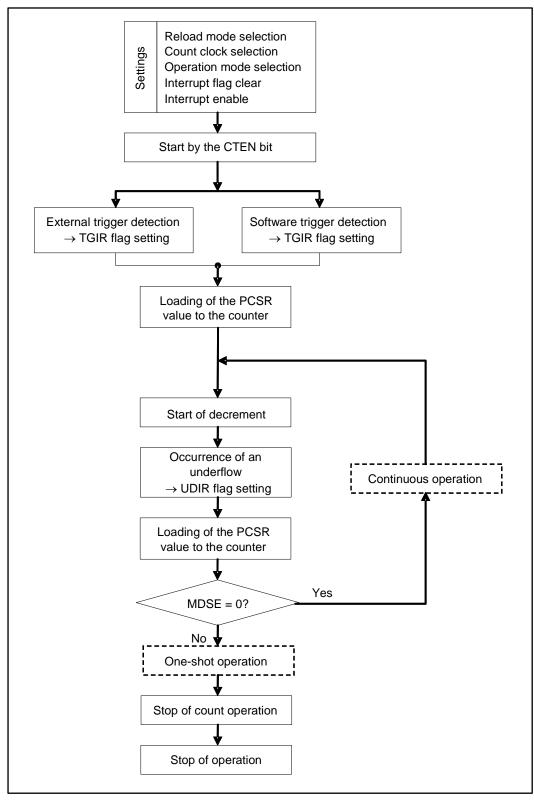

| 9.3.2. Reload Timer Operation Flowchart                                                  | 391     |

| 9.3.3. Timer Control Registers (TMCR and TMCR2) and Status Control Registe               |         |

| used when the Reload Timer is selected                                                   | 392     |

| 9.3.4. Cycle Set Register (PCSR)                                                         | 400     |

| 9.3.5. Timer Register (TMR)                                                              | 401     |

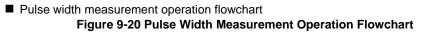

| 9.4. PWC timer function                                                                  | 402     |

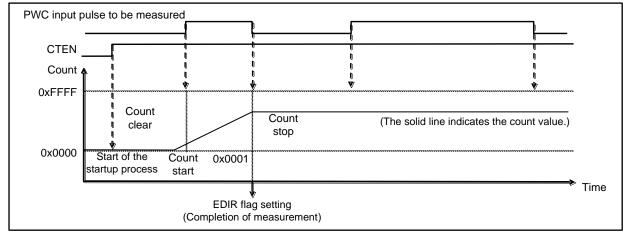

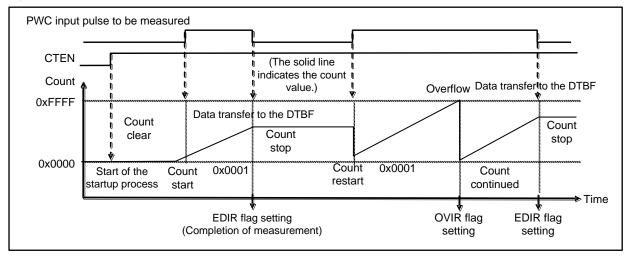

| 9.4.1. Operations of the PWC Timer                                                       | 403     |

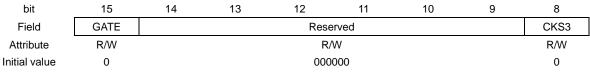

| 9.4.2. Timer Control Registers (TMCR and TMCR2) and Status Control Registe               | r (STC) |

| used when the PWC Timer is selected                                                      | 410     |

| 9.4.3. Data Buffer Register (DTBF)                                                       | 417     |

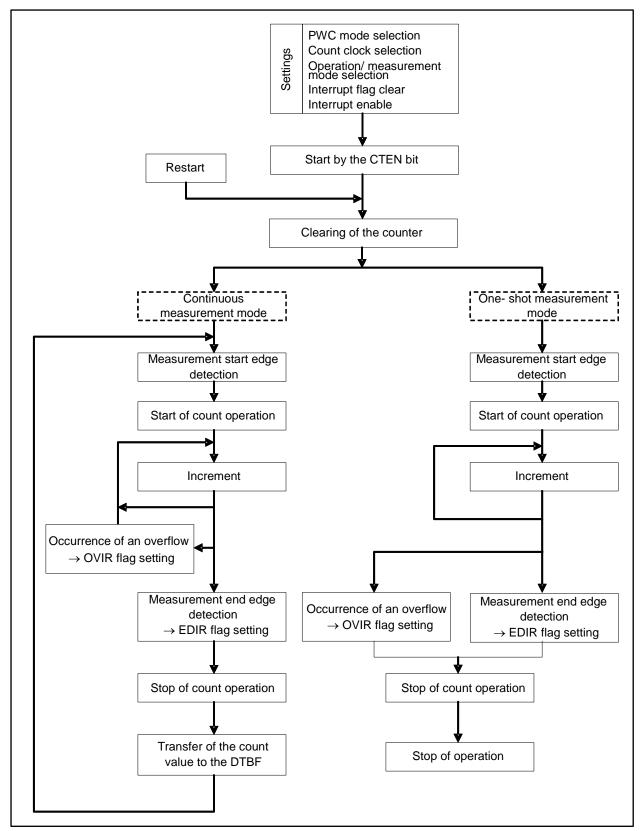

| CHAPTER 6: Multifunction Timer                                                           | 419     |

| 1. Overview of Multifunction Timer                                                       | 420     |

| 2. Configuration of Multifunction Timer                                                  |         |

| 2.1. Block Diagram of Multifunction Timer                                                | 422     |

| 2.1.1. Block Diagram                                                                     |         |

| 2.1.2. Outline of Function Blocks                                                        | 423     |

| 2.2. Description of Each Function Block                                                  |         |

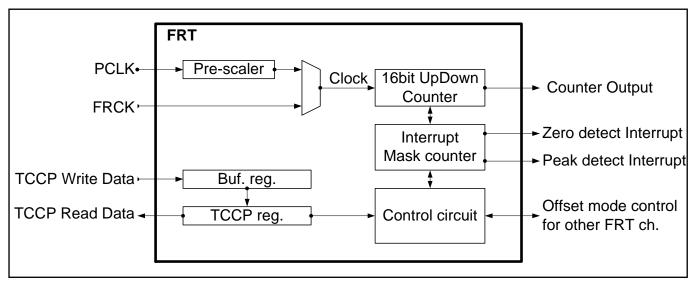

| 2.2.1. FRT: 3 channels                                                                   |         |

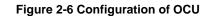

| 2.2.2. OCU: 6 Channels (2 channels × 3 units)                                            |         |

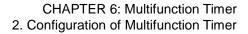

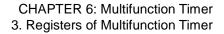

| 2.2.3. WFG: 3 Channels                                                                   |         |

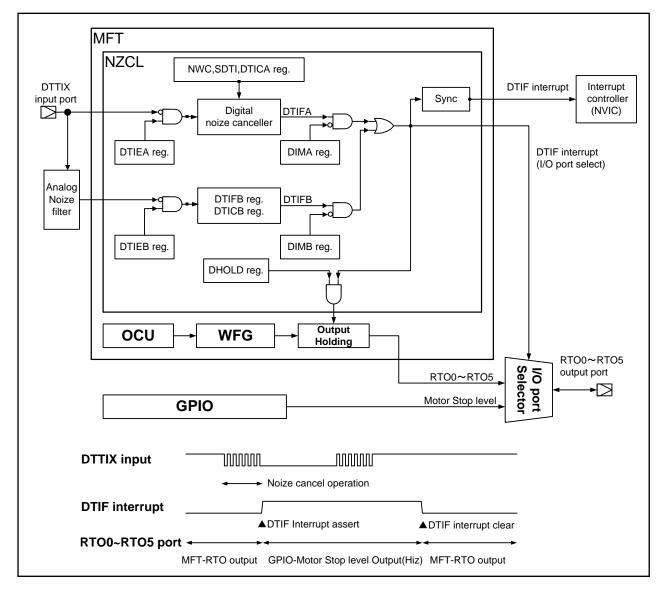

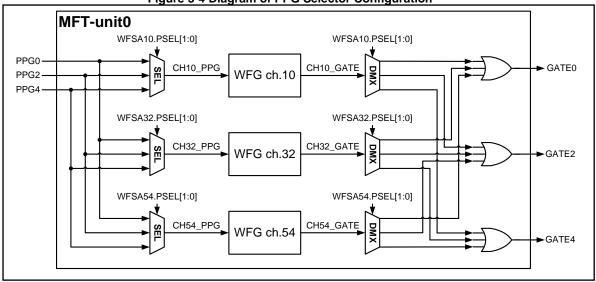

| 2.2.4. NZCL                                                                              |         |

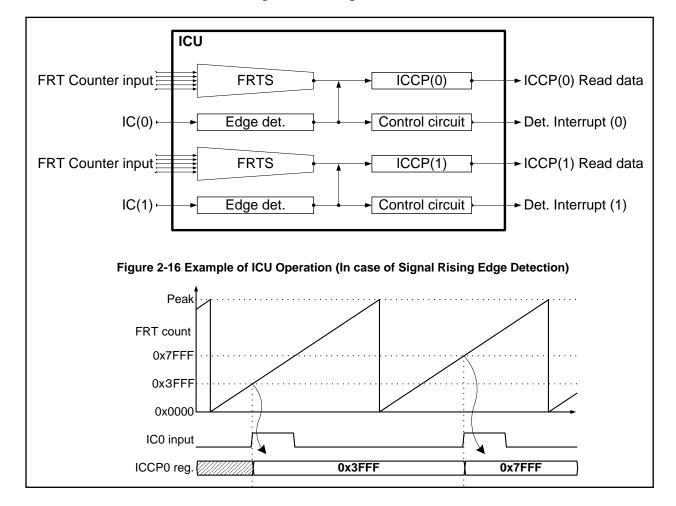

| 2.2.5. ICU: 4 Channels (2 channels × 2 units)                                            |         |

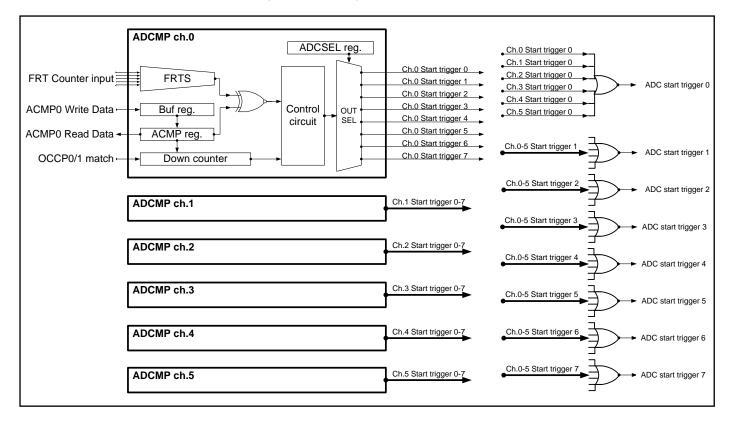

| 2.2.6. ADCMP: 6 Channels                                                                 |         |

| 2.3. I/O Pins of Multifunction Timer Unit                                                |         |

| 2.3.1. Correspondence with External I/O Pins                                             |         |

| 2.3.2. Interrupt Signal Outputs                                                          |         |

| 2.3.3. Other I/O Signal                                                                  |         |

| 2.4. Function Differences by Product Type                                                |         |

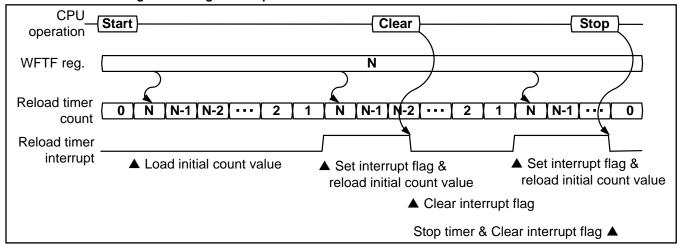

| 3. Registers of Multifunction Timer                                                      | 441     |

| 3.1. Individual Notations and Common Notations of Channel Numbers in Descriptions        |         |

| of Functions                                                                             |         |

| 3.2. List of Multifunction Timer Registers                                               |         |

| 3.3. Details of Register Functions                                                       |         |

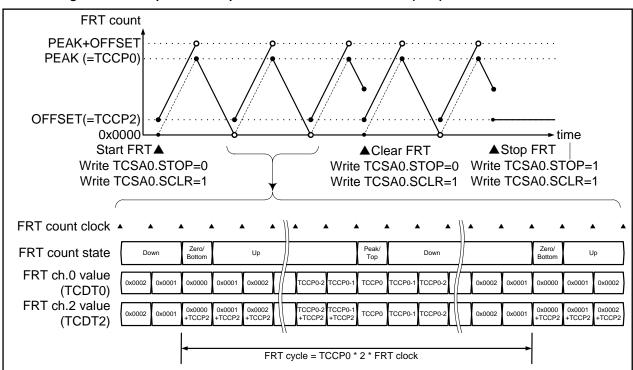

| 3.3.1. FRT Control Register A (TCSA)                                                     |         |

| 3.3.2. FRT Control Register C (TCSC)                                                     |         |

| 3.3.3. FRT Control Register D (TCSD) (Products after TYPE3-M4)                           |         |

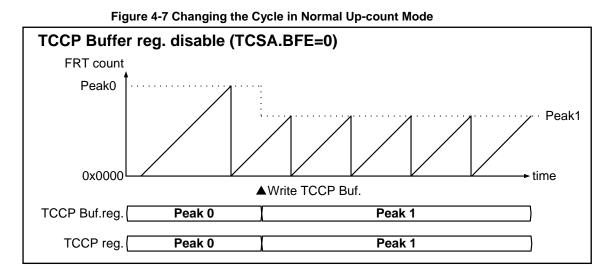

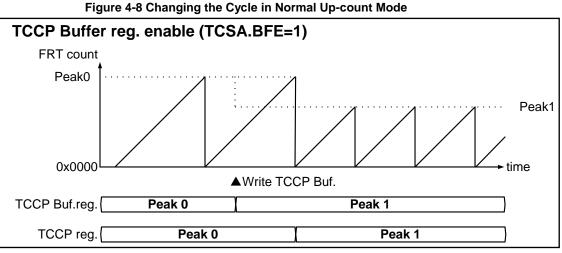

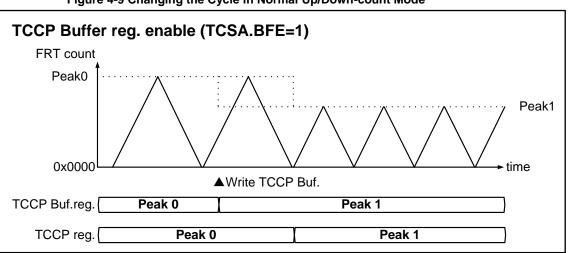

| 3.3.4. FRT Cycle Setting Register (TCCP)                                                 |         |

| 3.3.5. FRT Count Value Register (TCDT)                                                   |         |

| 3.3.6. FRT Simultaneous Start Control Register (TCAL)                                    |         |

| 3.3.7. OCU Connecting FRT Select Register (OCFS)<br>3.3.8. OCU Control Register A (OCSA) |         |

| 3.3.9. OCU Control Register B (OCSB)                                                     |         |

| 3.3.10. OCU Control Register C (OCSC)                                                    |         |

| 3.3.11. OCU Control Register D (OCSD) (TYPE1-M4, TYPE2-M4 products)                      |         |

| 3.3.12. OCU Control Register D (OCSD) (Products after TYPE3-M4)                          |         |

|                                                                                          |         |

| 3.3.13. OCU Control Register E (OCSE)<br>3.3.14. OCU Compare Value Store Register (OCCP) |         |

| 3.3.15. WFG Control Register A (WFSA)                                                    |         |

| 3.3.16. WFG Timer Value Register (WFTA/WFTB)                                             |         |

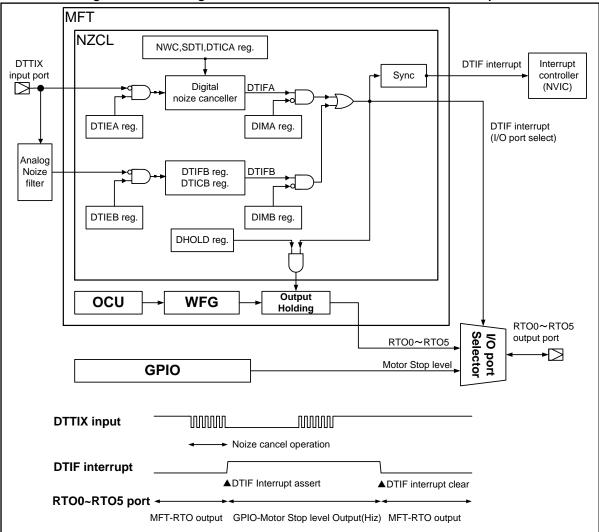

| 3.3.17. Pulse Counter Value Register (WFTF)                                              |         |

| 3.3.18. NZCL Control Register (NZCL)                                                     |         |

| 3.3.19. WFG Interrupt Control Register (WFIR)                                            |         |

| 3.3.20. ICU Connecting FRT Select Register (ICFS)                                        |         |

| 3.3.21. ICU Control Register A (ICSA)                                                    |         |

| 3.3.22. ICU Control Register B (ICSB)                                                    |         |

| 3.3.23. ICU Capture Value Store Register (ICCP)                                          |         |

|                                                                                          |         |

| 3.3.24. ADCMP Connecting FRT Select Register (ACFS)                                  | 504                                                                                                                        |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 3.3.25. ADCMP Control Register A (ACSA)                                              | 506                                                                                                                        |

| 3.3.26. ADCMP Control Register C (ACSC)                                              |                                                                                                                            |

| 3.3.27. ADCMP Control Register D (ACSD)                                              |                                                                                                                            |

| 3.3.28. ADCMP Compare Value Store Register (ACMP)                                    |                                                                                                                            |

| 3.3.29. ADCMP Mask Compare Value Storage Register (ACMC)                             |                                                                                                                            |

| 4. Operations of Multifunction Timer                                                 |                                                                                                                            |

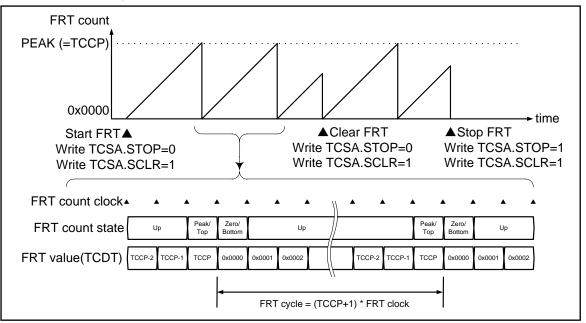

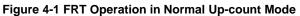

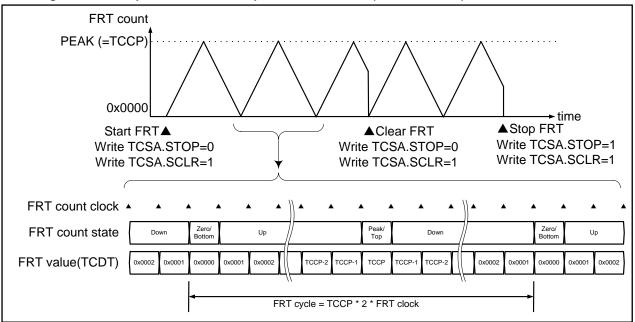

| 4.1. Descriptions of FRT Operation                                                   |                                                                                                                            |

| 4.1.1. FRT Control Register.                                                         |                                                                                                                            |

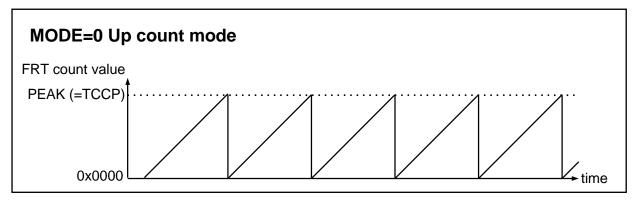

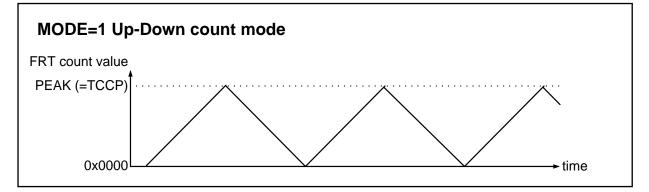

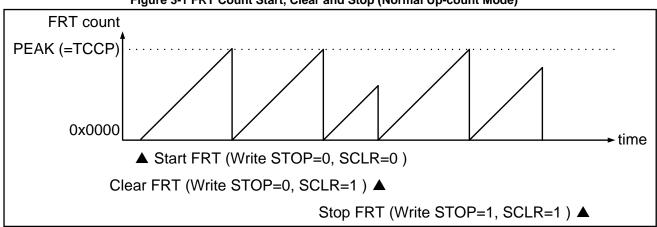

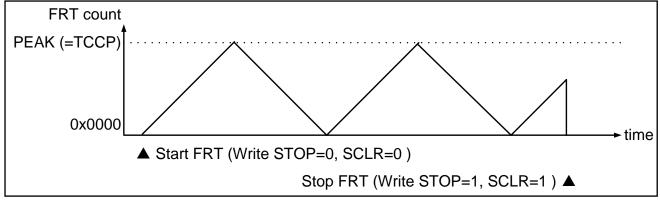

| 4.1.2. FRT Count Operation                                                           |                                                                                                                            |

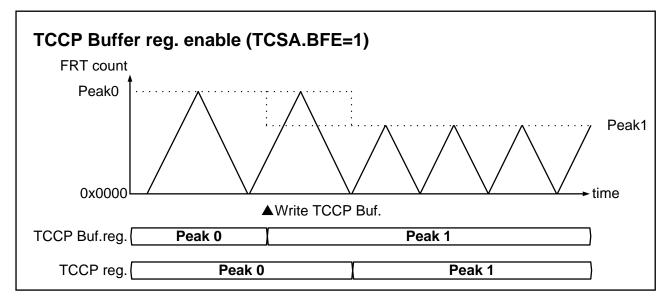

| 4.1.3. TCCP Register Function                                                        |                                                                                                                            |

| 4.1.4. FRT Interrupt Operation                                                       |                                                                                                                            |

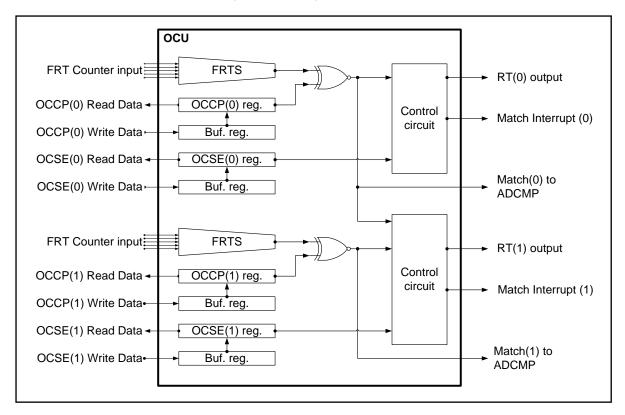

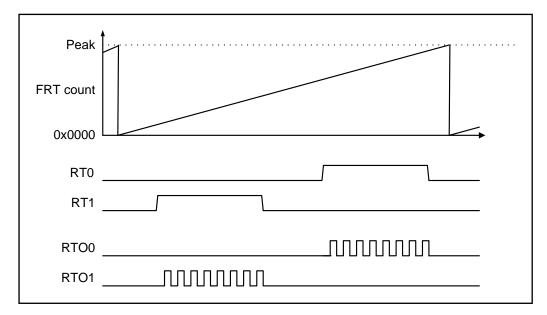

| 4.2. Description of OCU Operation                                                    |                                                                                                                            |

| 4.2.1. OCU Control Register                                                          |                                                                                                                            |

| 4.2.1. OCO Control Register                                                          |                                                                                                                            |

| ·                                                                                    |                                                                                                                            |

| 4.2.3. Channel-linked Operation                                                      |                                                                                                                            |

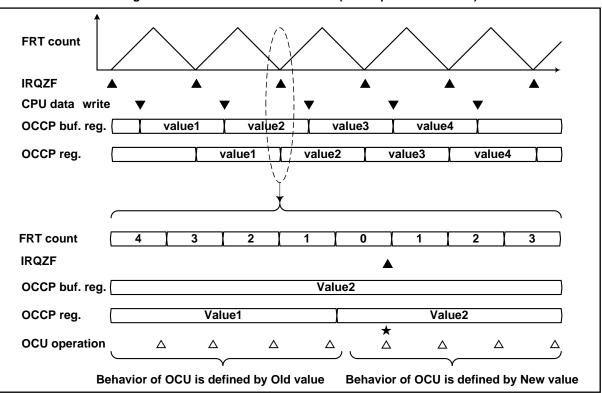

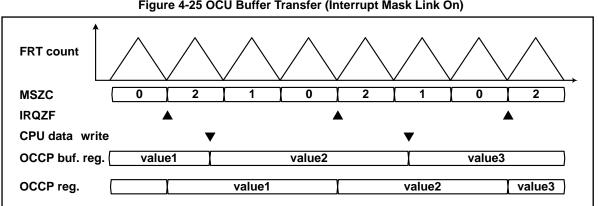

| 4.2.4. OCU Buffer Data Transfer                                                      |                                                                                                                            |

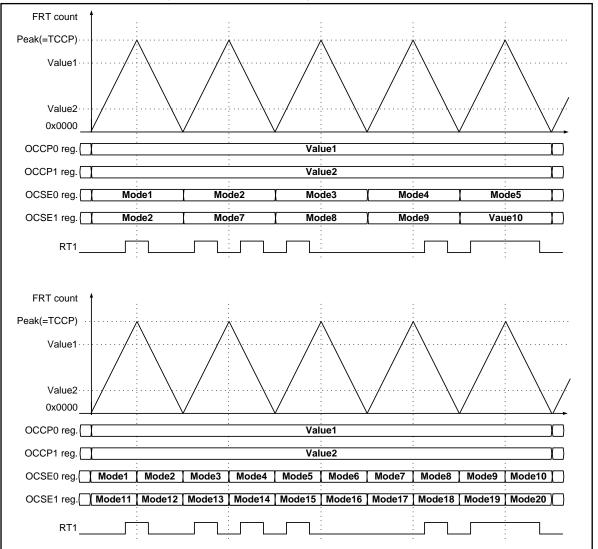

| 4.2.5. OCSE Buffer Function                                                          |                                                                                                                            |

| 4.3. OCU FM3 Family Product-compatible Operation                                     |                                                                                                                            |

| 4.3.1. OCU FM3 Family Product-compatible Operation                                   |                                                                                                                            |

| 4.4. Description of WFG Operation                                                    |                                                                                                                            |

| 4.4.1. WFG Control Register                                                          |                                                                                                                            |

| 4.4.2. List of CH_GATE Signal Output Details                                         |                                                                                                                            |

| 4.4.3. List of RTO0 to RTO5 Signal Output Details                                    |                                                                                                                            |

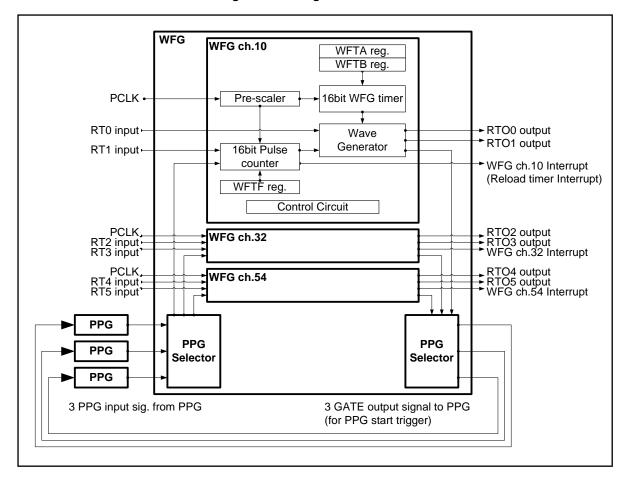

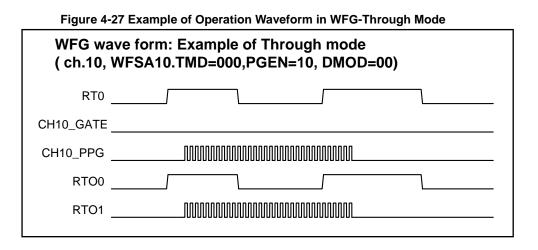

| 4.4.4. Through Mode                                                                  |                                                                                                                            |

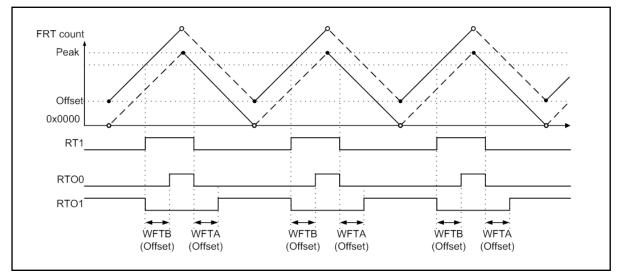

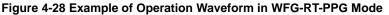

| 4.4.5. RT-PPG Mode                                                                   | 559                                                                                                                        |

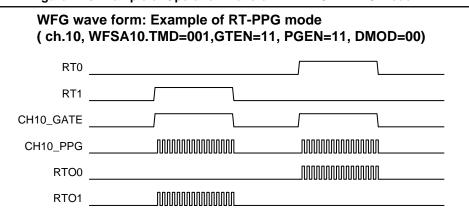

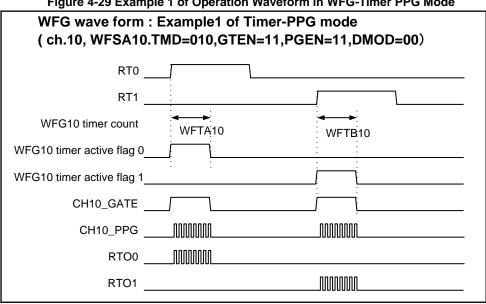

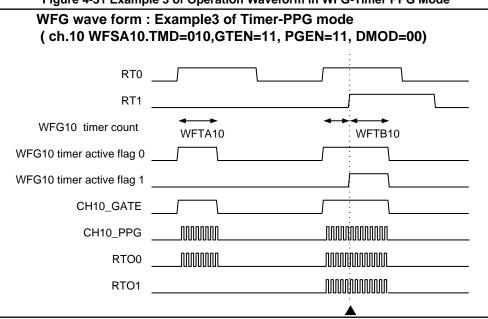

| 4.4.6. Timer-PPG Mode                                                                |                                                                                                                            |

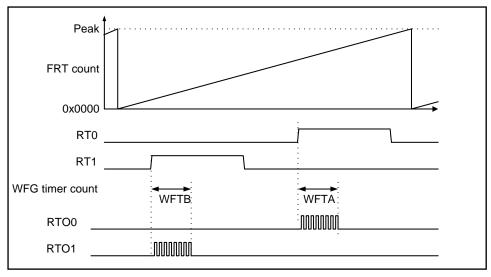

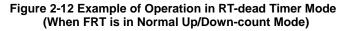

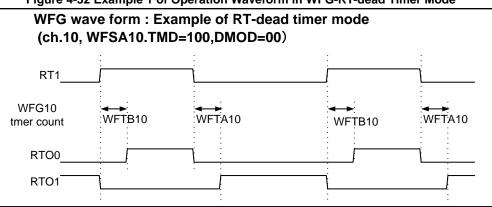

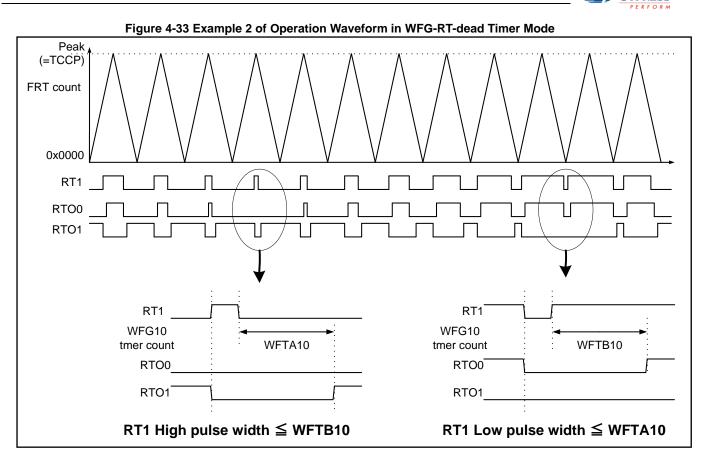

| 4.4.7. RT-dead Timer Mode                                                            |                                                                                                                            |

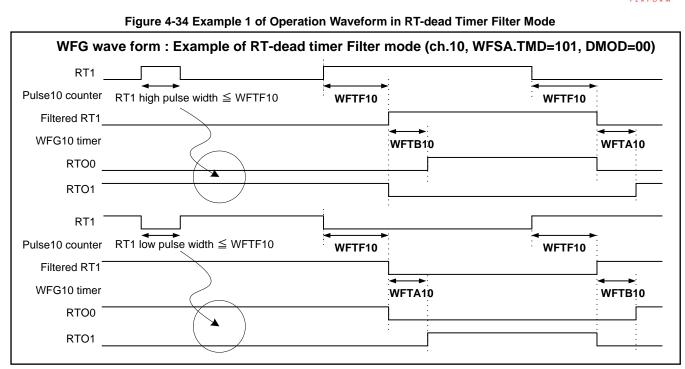

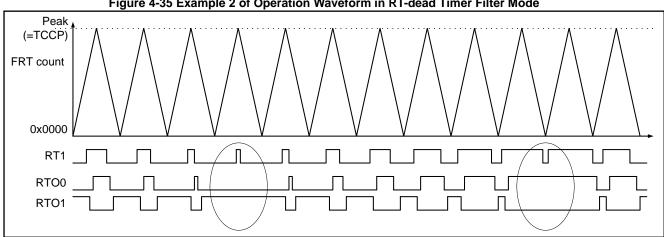

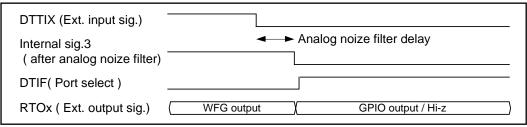

| 4.4.8. RT-dead Timer Filter Mode                                                     | 564                                                                                                                        |

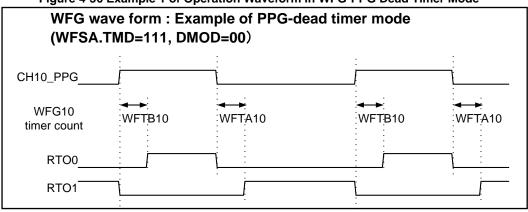

| 4.4.9. PPG-Dead Timer Mode                                                           | 566                                                                                                                        |

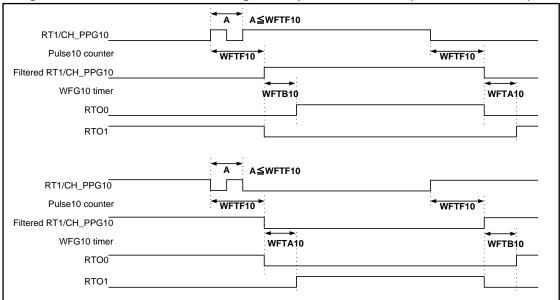

| 4.4.10. PPG-Dead Timer Filter Mode                                                   | 568                                                                                                                        |

| 4.4.11. Supplemental Explanation on Filtering Operation of Pulse Counter             | 569                                                                                                                        |

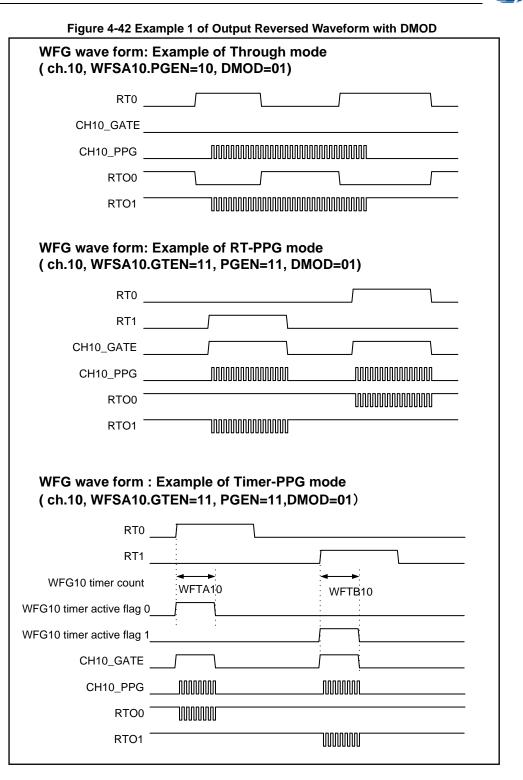

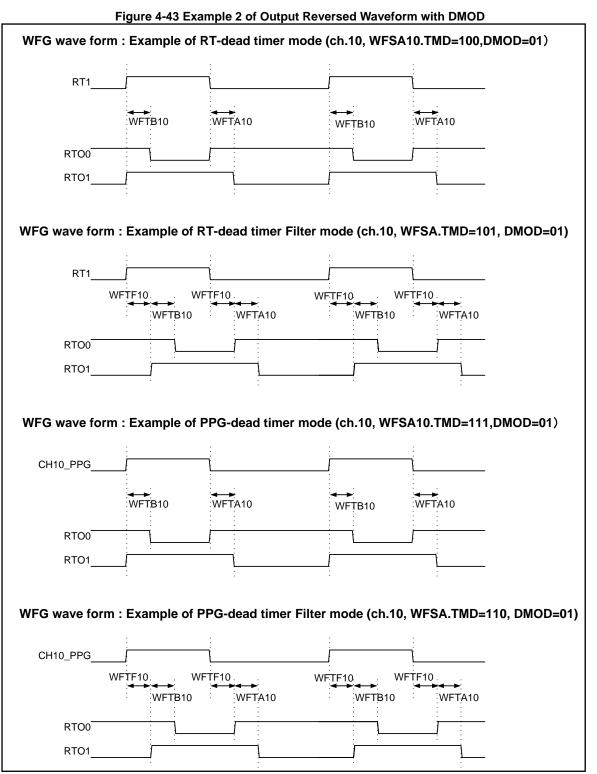

| 4.4.12. Output Polarity Revered by WESA.DMOD                                         |                                                                                                                            |

| 4.5. WFG FM3 Family Product-compatible Operation                                     |                                                                                                                            |

| 4.5.1. WFG Operation Compatible with FM3 Family Products                             |                                                                                                                            |

|                                                                                      |                                                                                                                            |

|                                                                                      | 575                                                                                                                        |

| 4.6. Description of ADCMP Operation<br>4.6.1. ADCMP Control Register                 |                                                                                                                            |

| 4.6.1. ADCMP Control Register                                                        | 575                                                                                                                        |

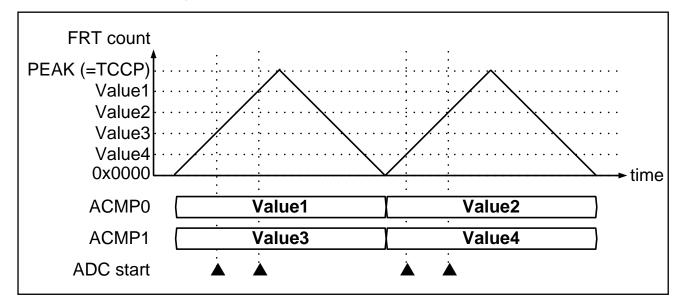

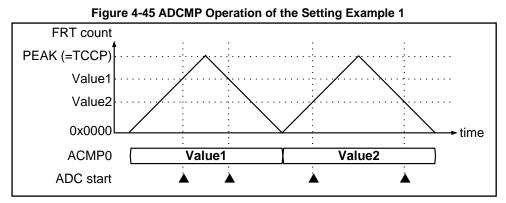

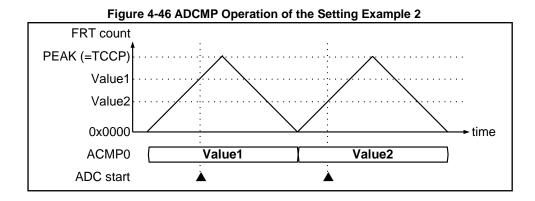

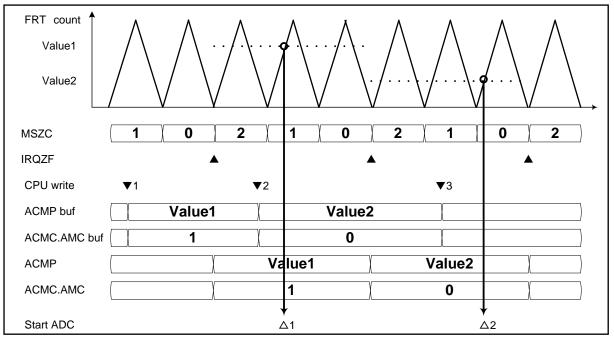

| 4.6.1. ADCMP Control Register<br>4.6.2. Normal Mode Operation                        | 575<br>576                                                                                                                 |

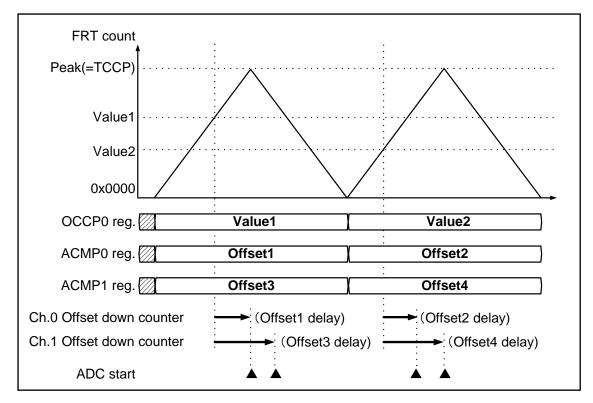

| <ul><li>4.6.1. ADCMP Control Register</li><li>4.6.2. Normal Mode Operation</li></ul> | 575<br>576<br>580                                                                                                          |

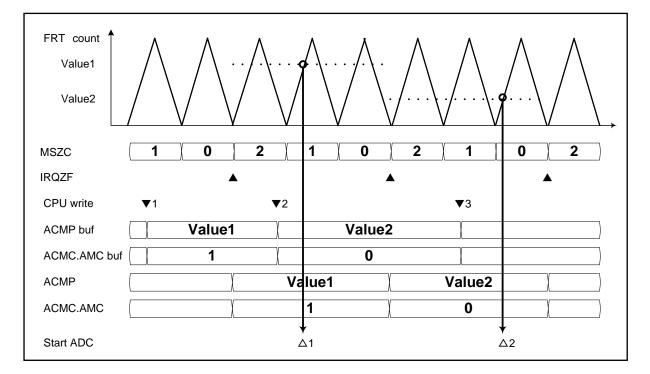

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583                                                                                                   |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585                                                                                            |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586                                                                                     |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587                                                                              |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587                                                                       |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587<br>589                                                                |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587<br>589<br>593                                                         |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587<br>589<br>593<br>596                                                  |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587<br>589<br>593<br>596<br>596                                           |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587<br>589<br>593<br>596<br>597                                           |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>587<br>589<br>593<br>596<br>597<br>598                                    |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>587<br>587<br>589<br>593<br>596<br>596<br>598<br>598<br>598                             |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>587<br>587<br>589<br>593<br>596<br>597<br>598<br>598<br>598<br>599                      |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>587<br>587<br>589<br>593<br>596<br>597<br>598<br>598<br>599<br>599<br>600               |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>587<br>587<br>589<br>593<br>596<br>596<br>597<br>598<br>598<br>599<br>600<br>601        |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>587<br>587<br>589<br>598<br>598<br>598<br>598<br>598<br>598<br>599<br>600<br>601<br>601 |

| <ul> <li>4.6.1. ADCMP Control Register</li></ul>                                     | 575<br>576<br>580<br>583<br>585<br>586<br>587<br>589<br>598<br>598<br>598<br>598<br>599<br>600<br>601<br>601<br>602        |

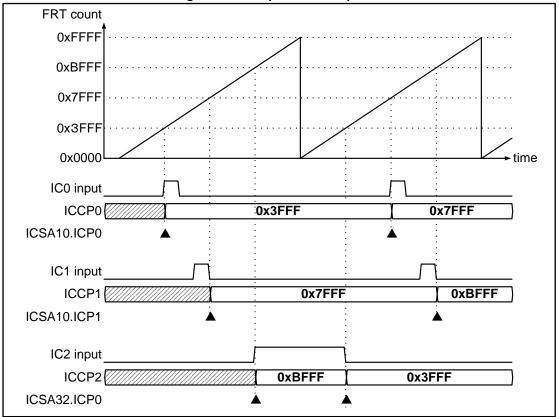

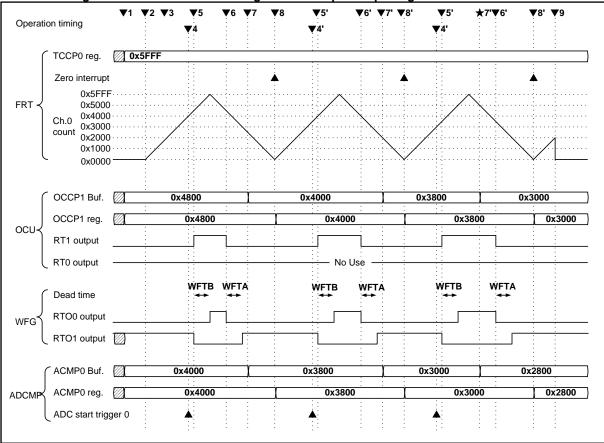

| 5.1.1. Timechart                                                          | 603 |

|---------------------------------------------------------------------------|-----|

| 5.1.2. FRT and OCU Settings and Operation                                 | 604 |

| 5.1.3. WFG Settings and Operation                                         | 605 |

| 5.1.4. ICU Settings and Operation                                         | 605 |

| 5.1.5. Completion of Process                                              | 605 |

| 5.1.6. Other Channel Processes                                            | 605 |

| 5.1.7. Details of Register Setting Values                                 | 606 |

| 5.2. Multifunction Timer Control Example 2                                |     |

| 5.2.1. Timechart                                                          |     |

| 5.2.2. FRT, OCU, and ADCMP Settings and Operation                         | 612 |

| 5.2.3. WFG Settings and Operation                                         |     |

| 5.2.4. Completion of Process                                              |     |

| 5.2.5. Details of Register Setting Values                                 |     |

| 6. Detailed Timing of Multifunction Timer Input/Output Signals            |     |

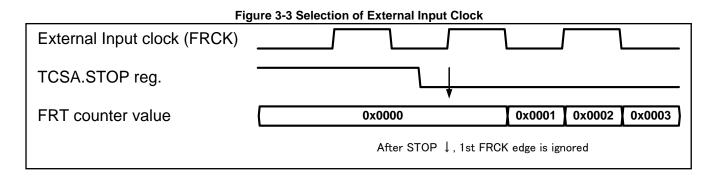

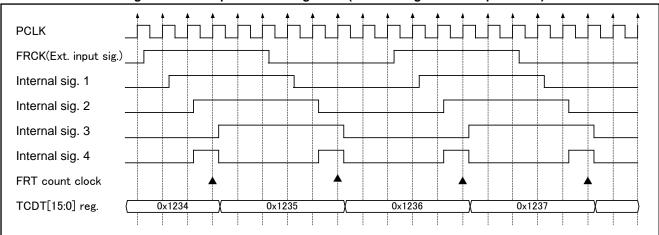

| 6.1. FRT Operation Detailed Timing When Using External Input Clock        |     |

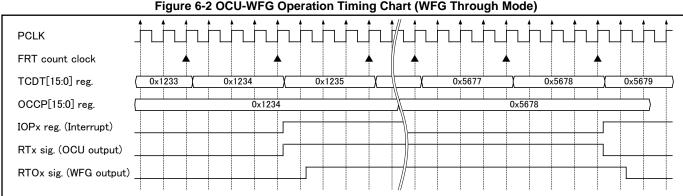

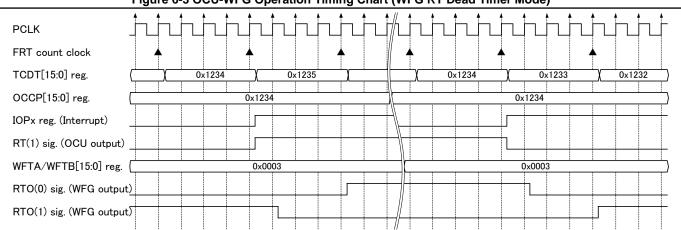

| 6.2. OCU and WFG Operation Detailed Timing                                |     |

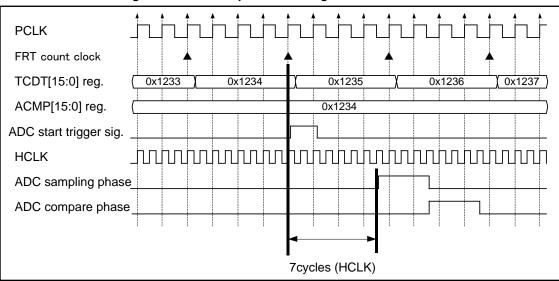

| 6.3. ADCMP Operation Detailed Timing                                      |     |

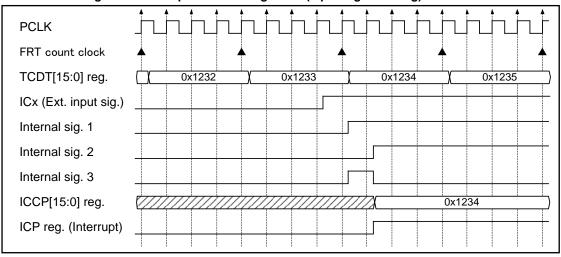

| 6.4. ICU Operation Detailed Timing                                        |     |

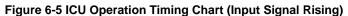

| 6.5. DTTIX Input Detailed Timing                                          |     |

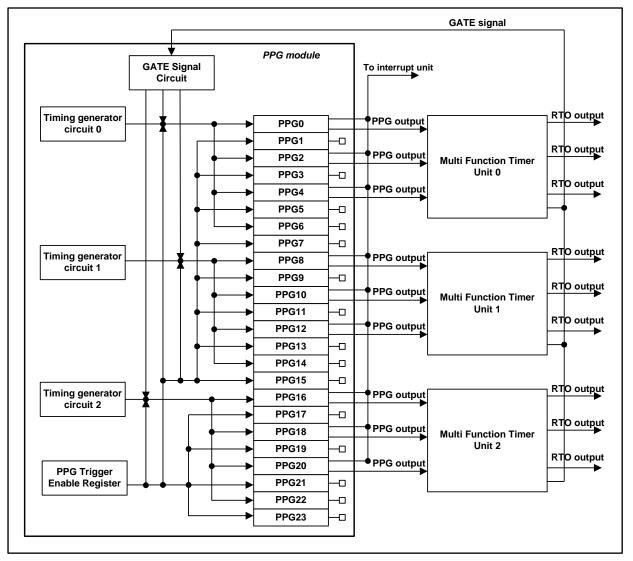

| CHAPTER 7-1: PPG Configuration                                            |     |

| 1. Configuration                                                          |     |

| CHAPTER 7-2: PPG                                                          |     |

| 1. Overview                                                               |     |

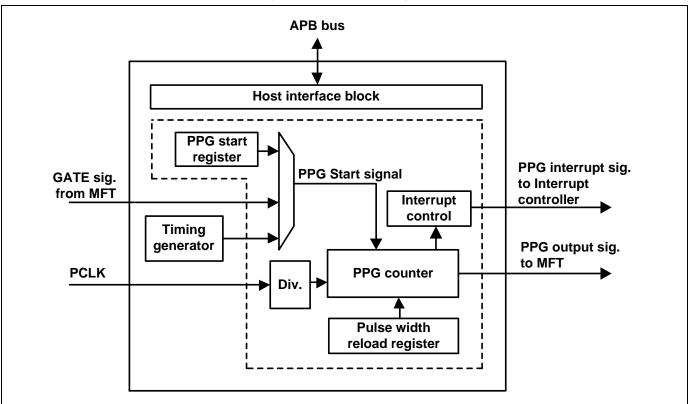

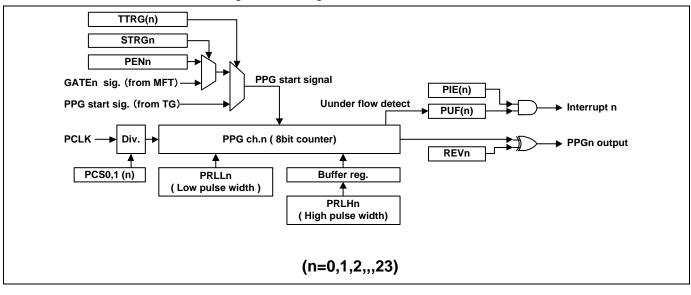

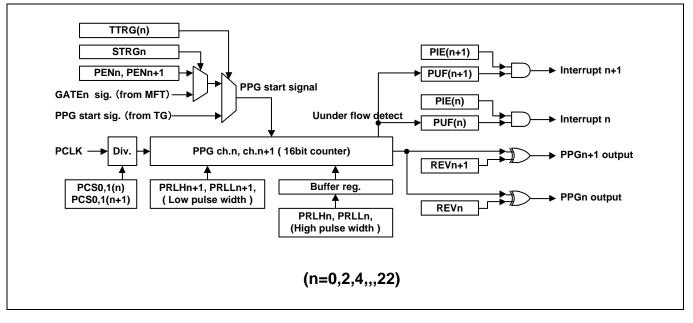

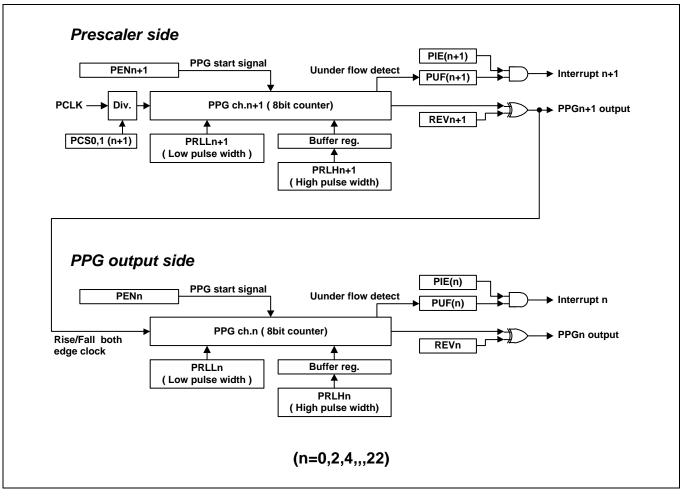

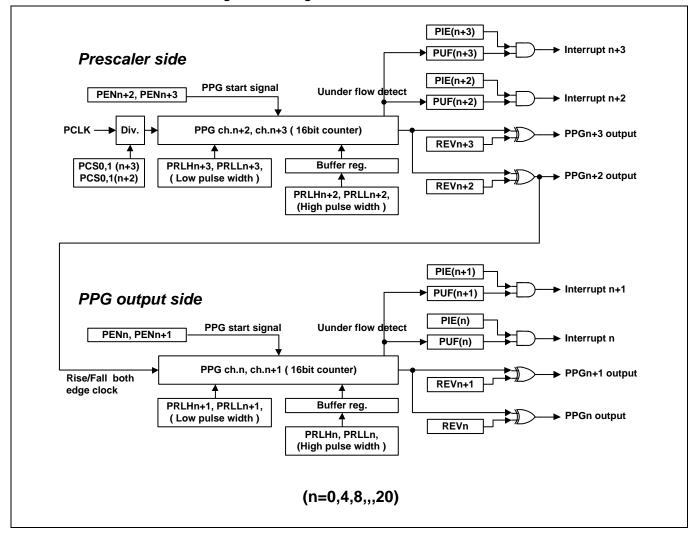

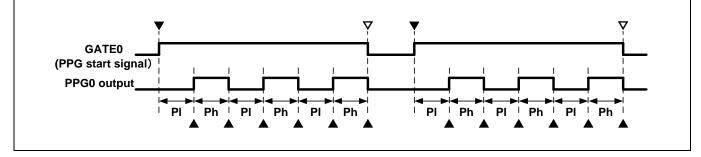

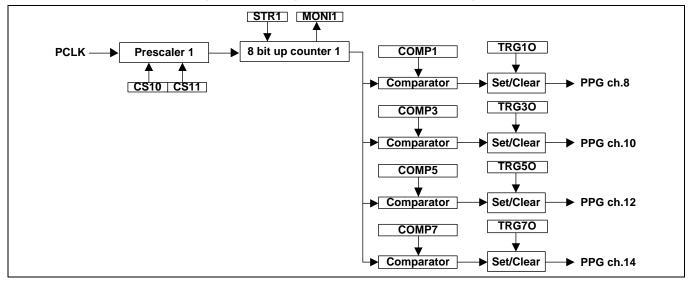

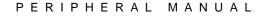

| 2. Configuration and Block Diagrams of PPG                                |     |

| 2.1. PPG Circuit Block Diagram                                            |     |

| 3. Operations of PPG                                                      |     |

| 3.1. PPG Circuit Operations                                               |     |

| •                                                                         |     |

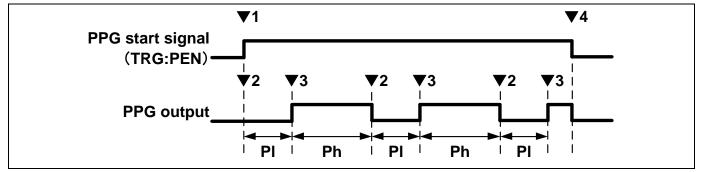

| 3.1.1. PPG Operations<br>3.1.2. PPG Operation Modes                       |     |

|                                                                           |     |

| 3.1.3. Selecting the PPG Operation Mode                                   |     |

| 3.1.4. Selecting the PPG Start Method                                     |     |

| 3.1.5. Selecting the Count Clock                                          |     |

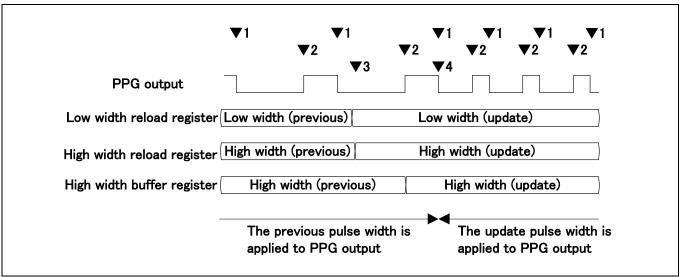

| 3.1.6. Specifying the Reload Register and Pulse Width                     |     |

| 3.1.7. Buffer Function of High Width Setting Reload Register              |     |

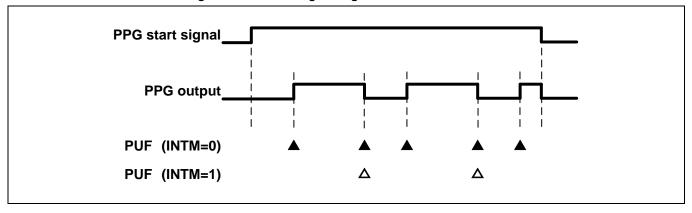

| 3.1.8. Interrupts                                                         |     |

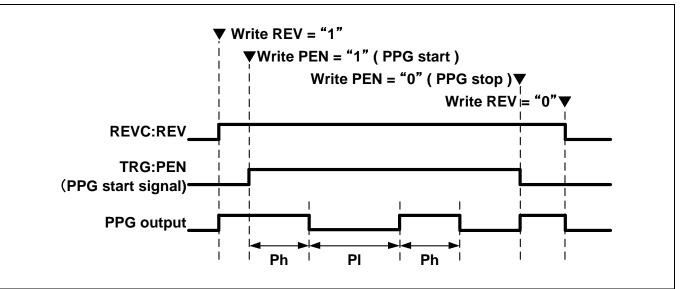

| 3.1.9. Polarity Reversal by REVn Register                                 |     |

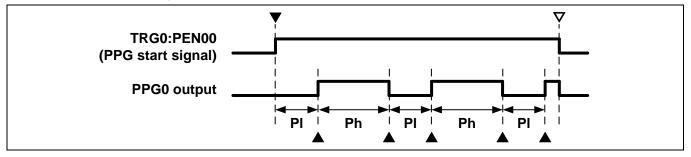

| 3.1.10. 8-bit PPG Operation Mode Example                                  |     |

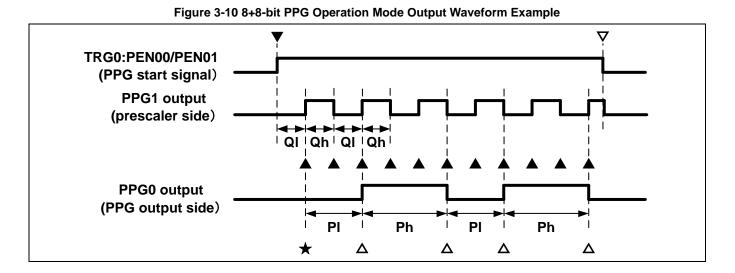

| 3.1.11. 8+8-bit PPG Operation Mode Example                                |     |

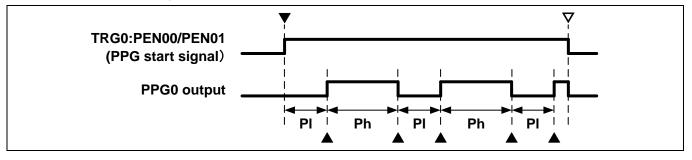

| 3.1.12. 16-bit PPG Operation Mode Example                                 |     |

| 3.1.13. 16+16-bit PPG Operation Mode Example                              |     |

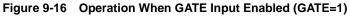

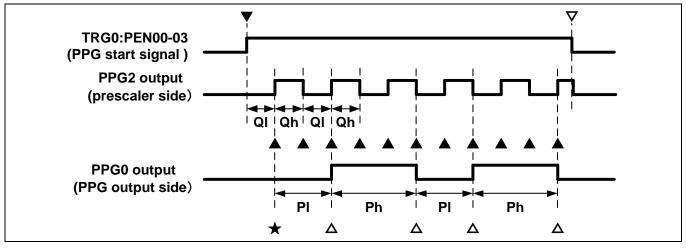

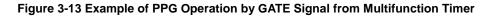

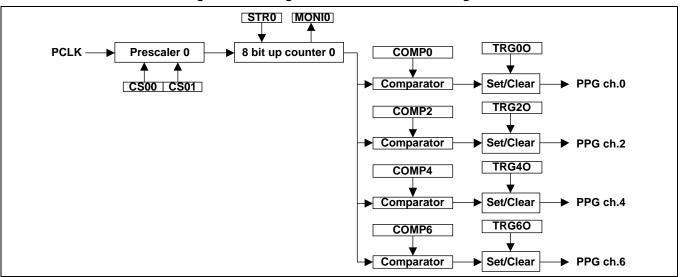

| 3.1.14. Example of PPG Operation by GATE Signals from Multifunction Timer |     |

| 3.2. Timing Generator Circuit Operations                                  |     |

| 3.2.1. Timing Generator Configuration                                     |     |

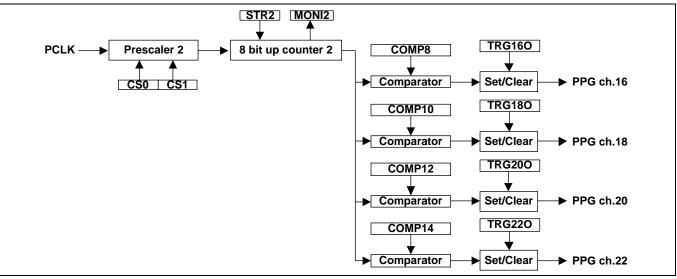

| 3.2.2. Timing Generator Operation Example                                 |     |

| 4. PPG Setup Procedure Example                                            |     |

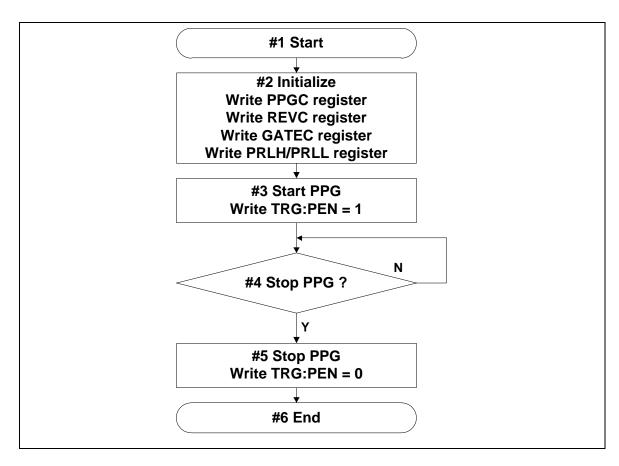

| 4.1. Example of PPG Start by Writing to PPG Start Register                |     |

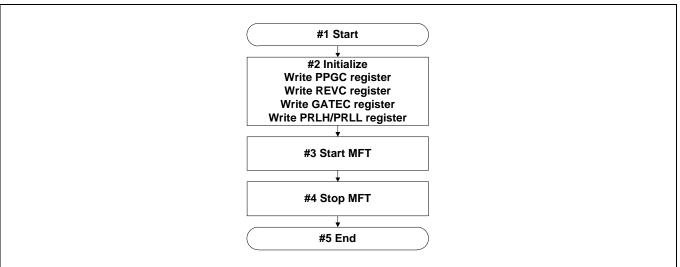

| 4.2. Example of PPG Start by GATE Signal from Multifunction Timer         |     |

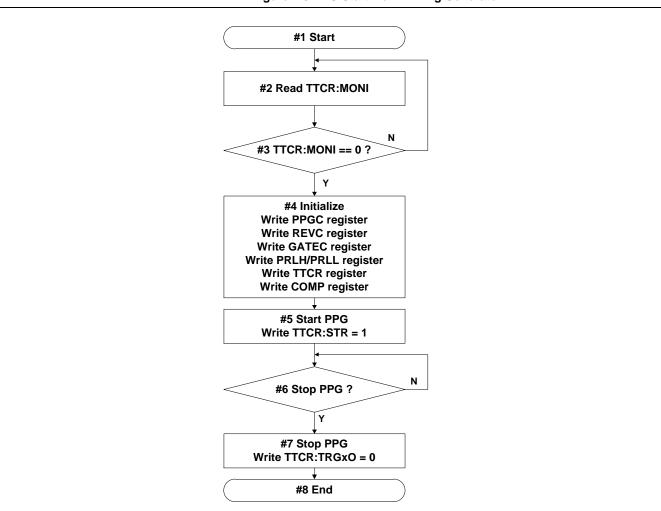

| 4.3. Example of PPG Start by Timing Generator                             | 656 |

| 5. PPG Registers                                                          |     |

| 5.1. Timing Generator PPG Start Trigger Control Register 0 (TTCR0)        |     |

| 5.2. Timing Generator PPG Start Trigger Control Register 1 (TTCR1)        | 661 |

| 5.3. Timing Generator PPG Start Trigger Control Register 2 (TTCR2)        | 662 |

| 5.4. Timing Generator PPG Compare Register "n" (COMPn, where n=0 to 14)   | 663 |

| 5.5. PPG Start Register 0 (TRG0)                                          | 664 |

| 5.6. PPG Start Register 1 (TRG1)                                          | 665 |

| 5.7. Output Reverse Register 0 (REVC0)                                    | 666 |

| 5.8. Output Reverse Register 1 (REVC1)                                    | 667 |

| 5.9. PPG Operation Mode Control Register n (PPGCn n=0 to 23)                   |       |

|--------------------------------------------------------------------------------|-------|

| 5.10. PPG Reload Registers n (PRLHn, PRLLn n=0 to 23)                          | . 671 |

| 5.11. Gate Function Control Registers n (GATEC0/GATEC4/GATEC8/GATEC12/GATEC16/ |       |

| GATEC20)                                                                       |       |

| 6. Notes on using PPG                                                          |       |

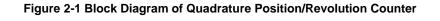

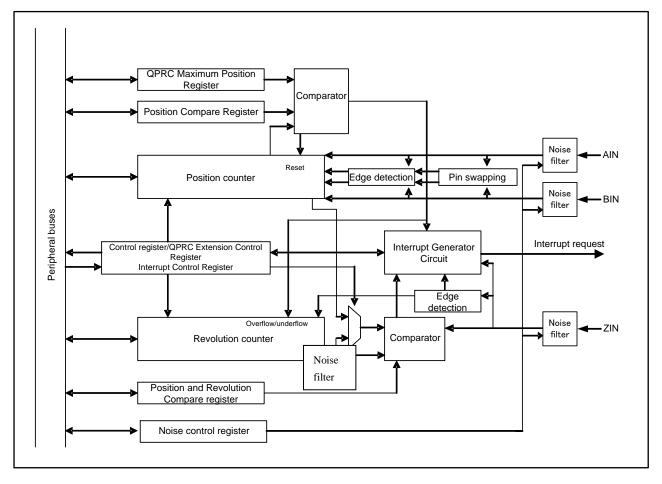

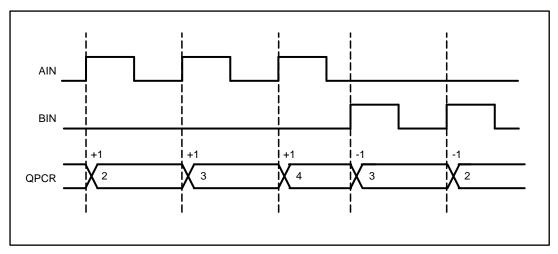

| CHAPTER 8-1: Quadrature Position/Revolution Counter                            |       |

| 1. Overview                                                                    |       |

| 2. Configuration                                                               |       |

| 3. Operations                                                                  |       |

| 4. Registers<br>4.1. QPRC Position Count Register (QPCR)                       |       |

| 4.1. QFRC Position Count Register (QFCR)                                       |       |

| 4.3. QPRC Position Counter Compare Register (QPCCR)                            |       |

| 4.4. QPRC Position and Revolution Counter Compare Register (QPRCR)             |       |

| 4.5. QPRC Control Register (QCR)                                               |       |

| 4.6. QPRC Extension Control Register (QECR)                                    |       |

| 4.7. Low-Order Bytes of QPRC Interrupt Control Register (QICRL)                |       |

| 4.8. High-Order Bytes of QPRC Interrupt Control Register (QICRH)               |       |

| 4.9. QPRC Maximum Position Register (QMPR)                                     |       |

| 4.10. AIN Noise Control Register (NFCTLA)                                      | . 717 |

| 4.11. BIN Noise Control Register (NFCTLB)                                      | . 718 |

| 4.12. ZIN Noise Control Register (NFRCTLZ)                                     |       |

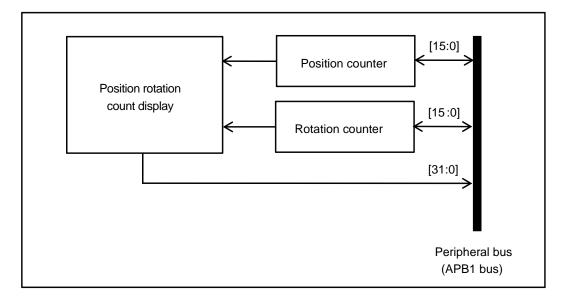

| CHAPTER 8-2: Quad Counter Position Rotation Count Display Function             |       |

| 1. Overview and Configuration                                                  |       |

| 2. Register                                                                    |       |

| 2.1. Quad Counter Position Rotation Count Register (QPRCRR)                    |       |

| Appendixes                                                                     |       |

| A. Register Map                                                                |       |

| 1. Register Map                                                                |       |

| 1.1. FLASH_IF<br>1.1.1. TYPE1-M4, TYPE2-M4 products                            |       |

| 1.1.2. TYPE3-M4 product                                                        |       |

| 1.1.3. TYPE4-M4, TYPE5-M4, TYPE6-M4 products                                   |       |

| 1.2. Unique ID                                                                 |       |

| 1.3. ECC Capture Address                                                       |       |

| 1.4. Clock/Reset                                                               |       |

| 1.4.1. TYPE1-M4, TYPE2-M4 products                                             | . 733 |

| 1.4.2. TYPE3-M4, TYPE4-M4, TYPE5-M4, TYPE6-M4 products                         | . 735 |

| 1.5. HW WDT                                                                    | . 737 |

| 1.6. SW WDT                                                                    | -     |

| 1.7. Dual_Timer                                                                |       |

| 1.8. MFT                                                                       |       |

| 1.8.1. TYPE1-M4, TYPE2-M4 products                                             |       |

| 1.8.2. TYPE3-M4, TYPE4-M4, TYPE5-M4, TYPE6-M4 products                         |       |

| 1.9. PPG                                                                       |       |

| 1.10. Base Timer<br>1.11. IO Selector for Base Timer                           |       |

| 1.11. 10 Selector for Base Timer                                               |       |

| 1.12.1. TYPE1-M4, TYPE2-M4, TYPE6-M4 products                                  |       |

| 1.12.2. TYPE3-M4, TYPE4-M4, TYPE5-M4 products                                  |       |

| 1.13. QPRC NF                                                                  |       |

| 1.14. A/DC                                                                     |       |

| 1.15. CR Trim                                                                  |       |

| 1.16. EXTI                                                                     |       |

| 1.16.1. TYPE1-M4, TYPE2-M4, TYPE3-M4, TYPE4-M4 products                        | . 755 |

| 1.16.2. TYPE5-M4, TYPE6-M4 products                                            |       |

| 1.17. INT-Req. READ                                                            | . 756 |

|   | 1.17.1. TYPE1-M4, TYPE2-M4, TYPE6-M4 products              | 756 |

|---|------------------------------------------------------------|-----|

|   | 1.17.2. TYPE3-M4, TYPE5-M4 product                         |     |

|   | 1.17.3. TYPE4-M4 product                                   |     |

|   | 1.18. D/AC                                                 |     |

|   | 1.19. HDMI-CEC                                             |     |

|   | 1.20. GPIO                                                 | 778 |

|   | 1.20.1. TYPE1-M4, TYPE2-M4, TYPE6-M4 products              | 778 |

|   | 1.20.2. TYPE3-M4 product                                   |     |

|   | 1.20.3. TYPE4-M4 product                                   |     |

|   | 1.20.4. TYPE5-M4 product                                   | 802 |

|   | 1.21. LVD                                                  | 811 |

|   | 1.22. DS_Mode                                              | 811 |

|   | 1.23. USB Clock                                            | 812 |

|   | 1.24. CAN_Prescaler                                        | 813 |

|   | 1.25. MFS                                                  | 813 |

|   | 1.26. CRC                                                  | 815 |

|   | 1.27. Watch Counter                                        | 815 |

|   | 1.28. RTC                                                  | 816 |

|   | 1.28.1. TYPE1-M4, TYPE2-M4, TYPE3-M4, TYPE6-M4 products    | 816 |

|   | 1.28.2. TYPE4-M4 product                                   | 819 |

|   | 1.28.3. TYPE5-M4 product                                   | 823 |

|   | 1.29. Low-speed CR Prescaler                               | 824 |

|   | 1.30. Peripheral Clock Gating                              | 825 |

|   | 1.30.1. TYPE1-M1, TYPE2-M4 products                        | 825 |

|   | 1.30.2. TYPE3-M4, TYPE4-M4 products                        |     |

|   | 1.30.3. TYPE5-M4, TYPE6-M4 products                        |     |

|   | 1.31. Smart Card Interface                                 |     |

|   | 1.32. MFSI2S                                               | 828 |

|   | 1.33. I2S Prescaler                                        |     |

|   | 1.33.1. TYPE1-M4, TYPE2-M4, TYPE3-M4 products              |     |

|   | 1.33.2. TYPE4-M4 product                                   |     |

|   | 1.34. GDC_Prescaler                                        |     |

|   | 1.35. EXT-Bus I/F                                          |     |

|   | 1.35.1. TYPE1-M4 product                                   |     |